ADSP-214xx SHARC Processor Hardware Reference 9-23

Digital Application/Digital Peripheral Interfaces

Listing 9-3. SRU Connection SPORT/PCG to MISC/DAI Pin Buffers

SRU(HIGH, PBEN03_I); // DAI pin 3 output

nop;

SRU(DAI_PB14_O, DAI_PB03_I); // connect pin 3 and 14

nop;

SRU(PCG_CLKB_O, DAI_PB14_I); // connect PCG and pin 14

nop;

SRU(SPORT2_FS_O, MISCA4_I); // connect SPORT to MISCA

nop;

SRU(MISCA4_O, PBEN14_I); // connect MISCA to PBEN14

nop;

SRU(HIGH, INV_MISCA4_I); // invert MISCA4 input

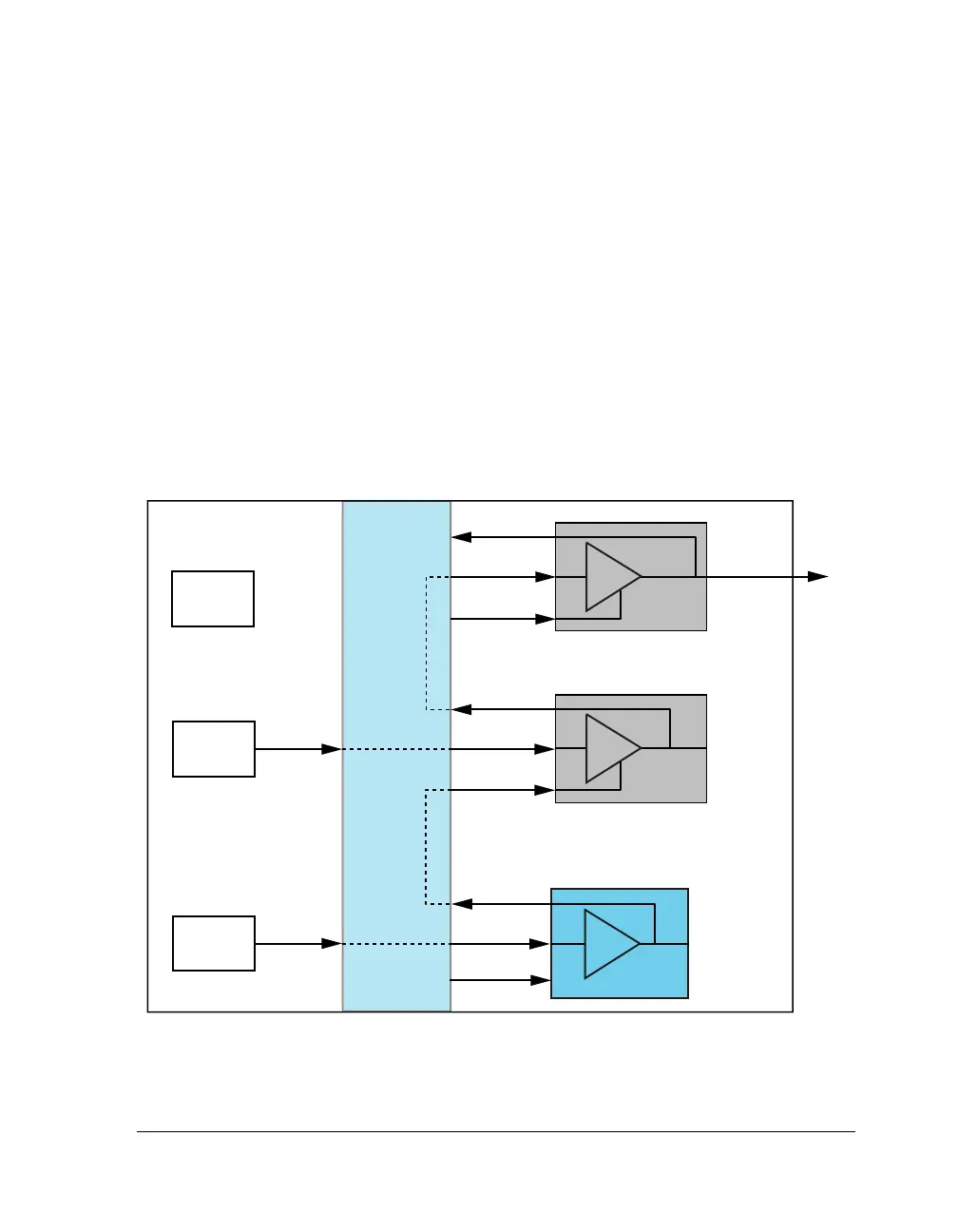

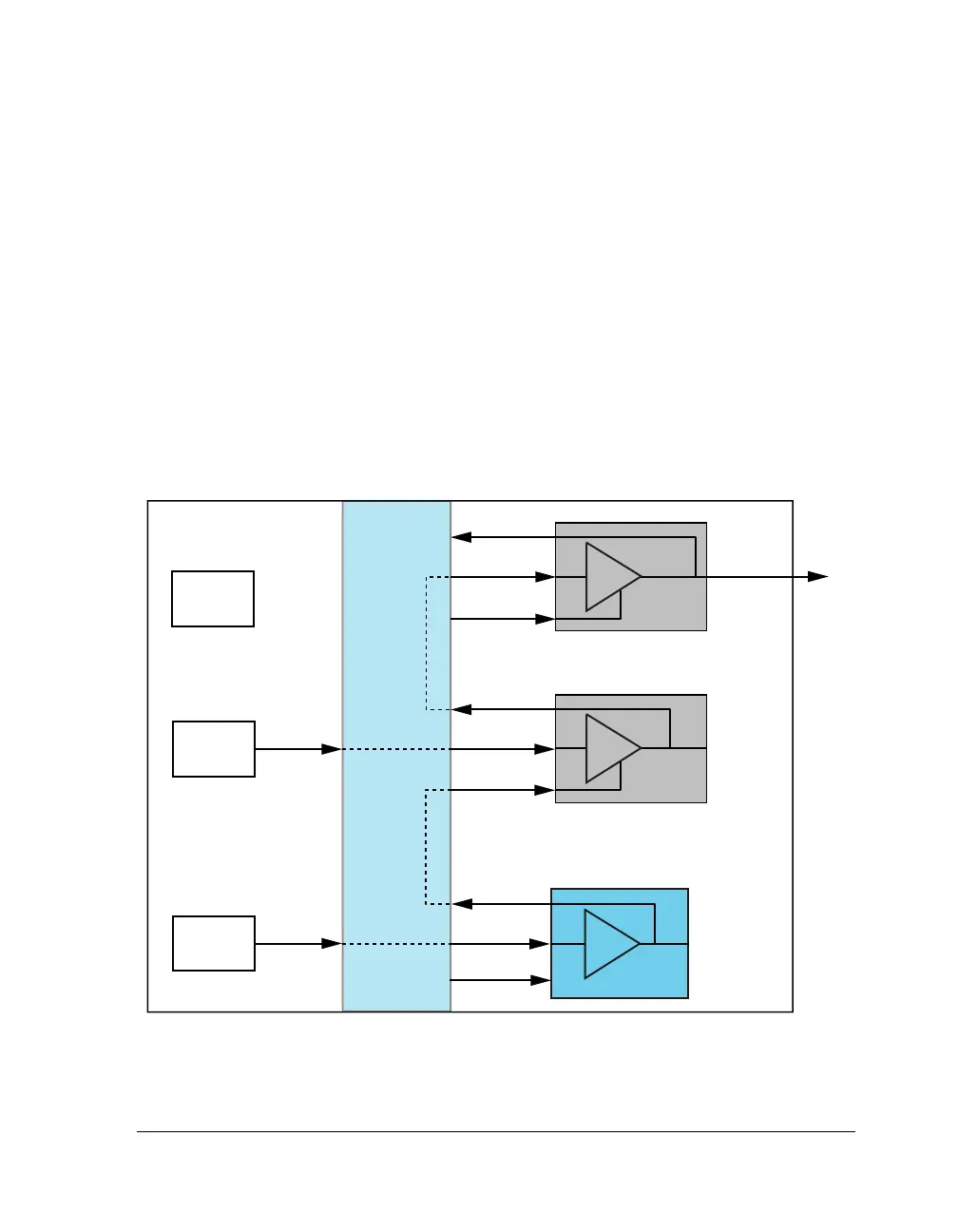

Figure 9-12. SRU Connection SPORT/PCG to MISC/DAI Pin Buffers

SRU

PBEN03_I

DAI_PB03_O

DAI_PB14

DAI_PB03

MISCA4

PERIPHERAL

PCG B

SPORT2

PCG_CLKB_O

SPORT2_FS_O

DAI_PB03_I

PBEN14_I

DAI_PB14_O

DAI_PB14_I

MISCA4_I

MISCA4_O

INVERT

Loading...

Loading...