IIR Accelerator

6-58 ADSP-214xx SHARC Processor Hardware Reference

The accelerator has the following logical sub blocks:

• A data path unit with the following elements:

• 32/40-bit coefficient memory for storing biquad coefficients

• 32/40-bit data memory for the intermediate data

• One 40/32-bit floating-point multiplier and adder (MAC)

unit

• An input data buffer to efficiently supply data to MAC

• One 40-bit result register to hold result of biquad

• Configuration registers for controlling various parameters such as

the number of biquads, the number of channels, interrupt control,

and DMA control

• A core access interface for writing the DMA/filter configuration

registers and for reading the status registers

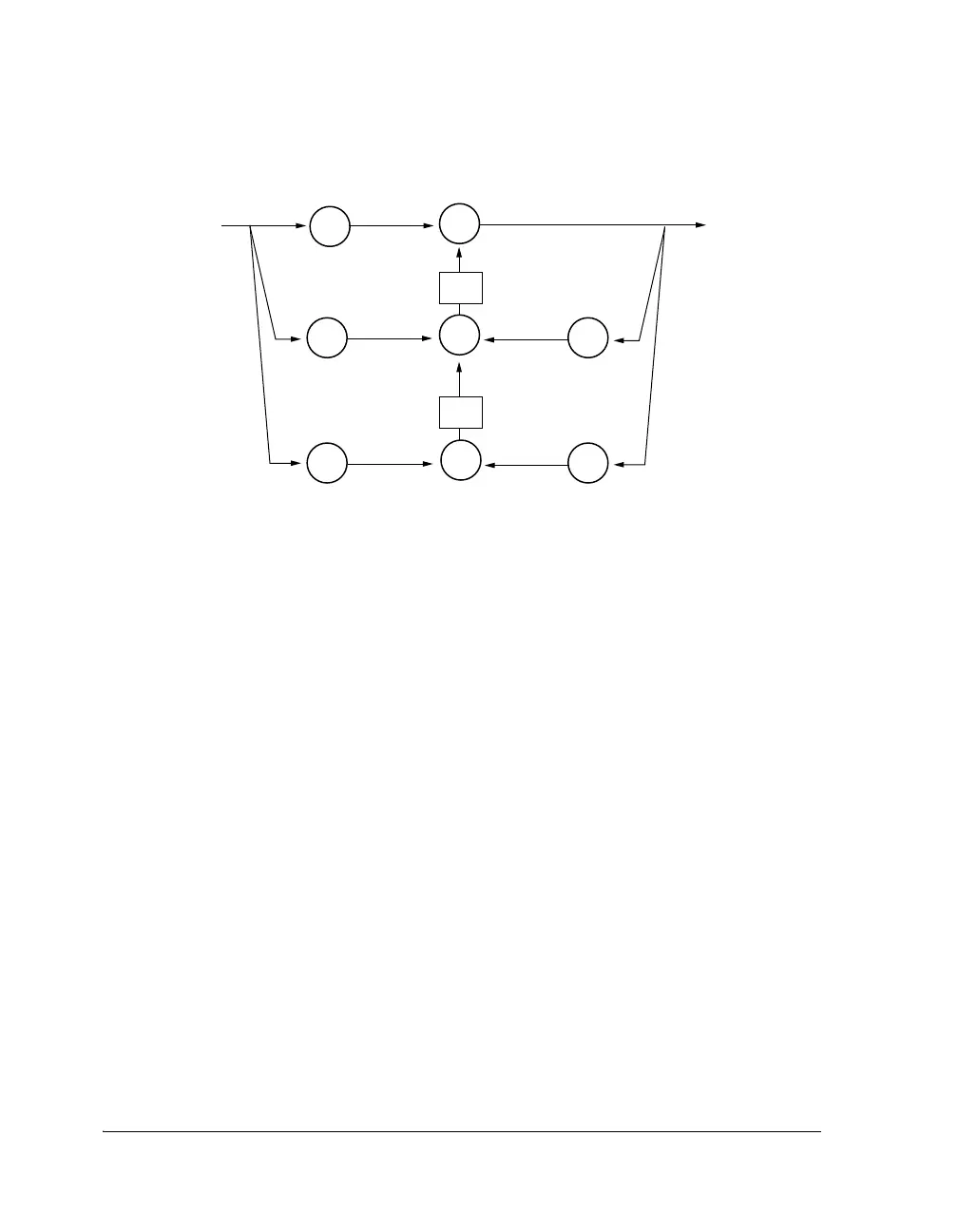

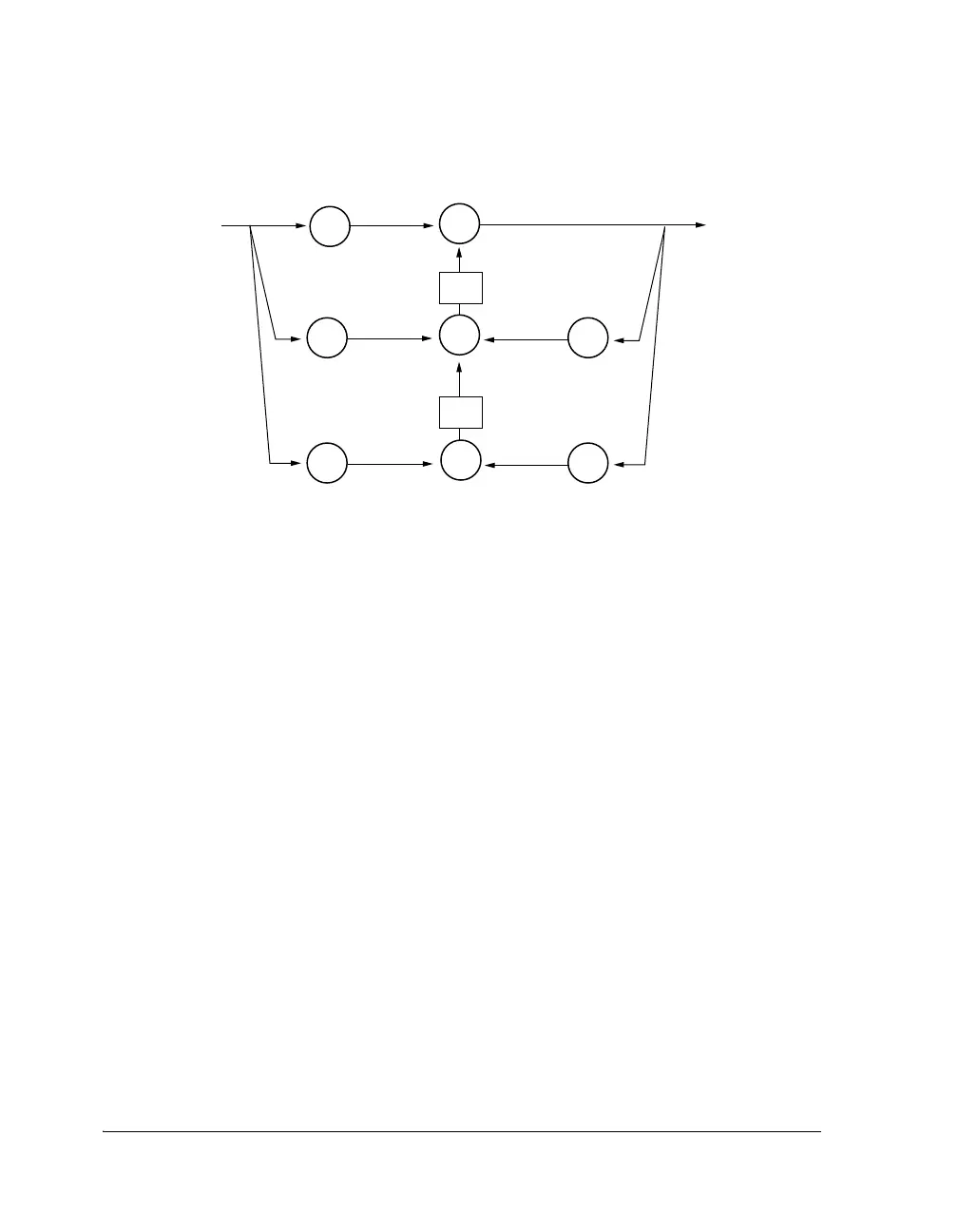

Figure 6-10. Transposed Direct Form II Biquad

k0

a

k1

a

k2

d

k1

d

k2

b

k1

b

k2

y

k

Z

-1

Z

-1

+

x

k

Loading...

Loading...