ADSP-214xx SHARC Processor Hardware Reference 6-57

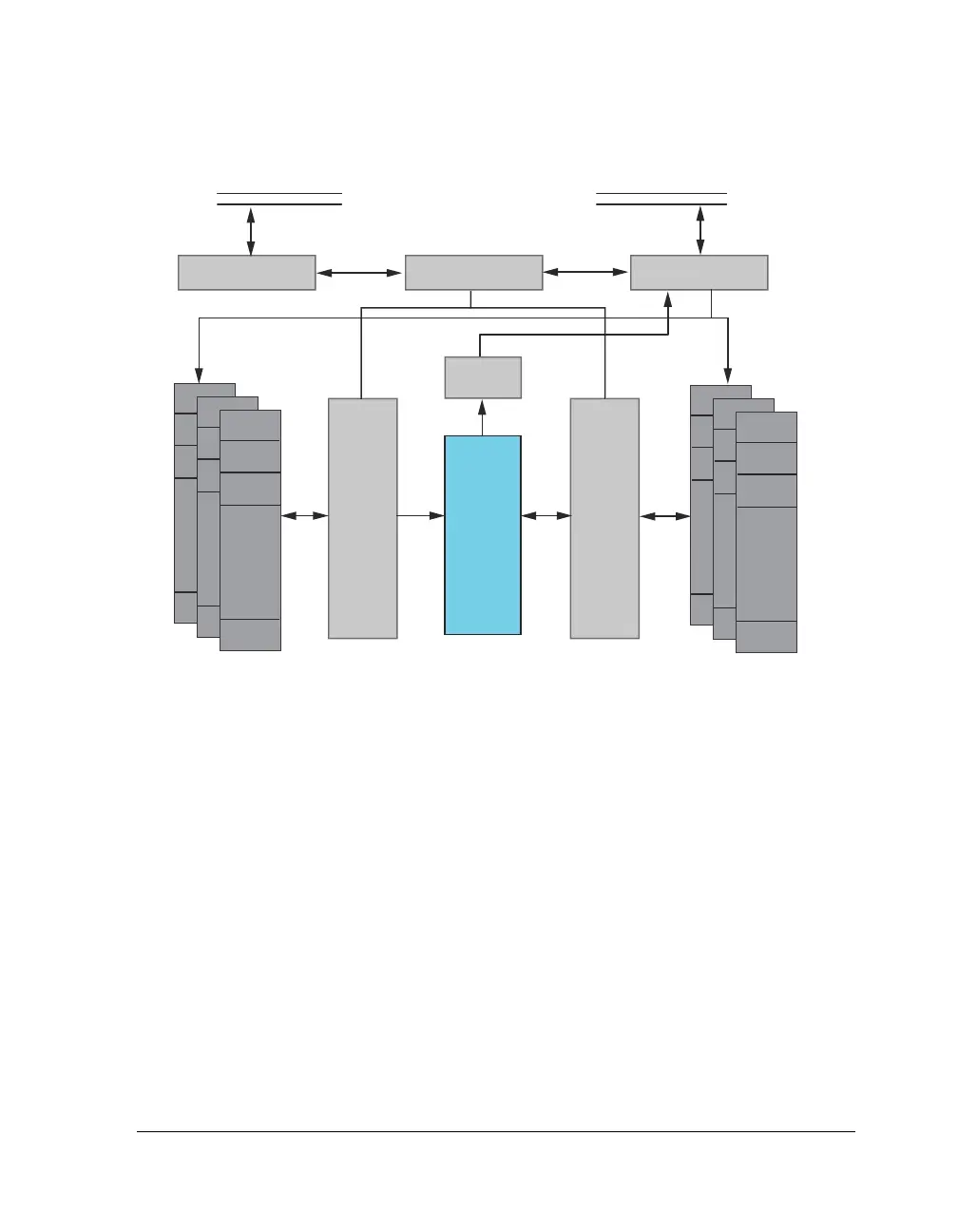

FFT/FIR/IIR Hardware Modules

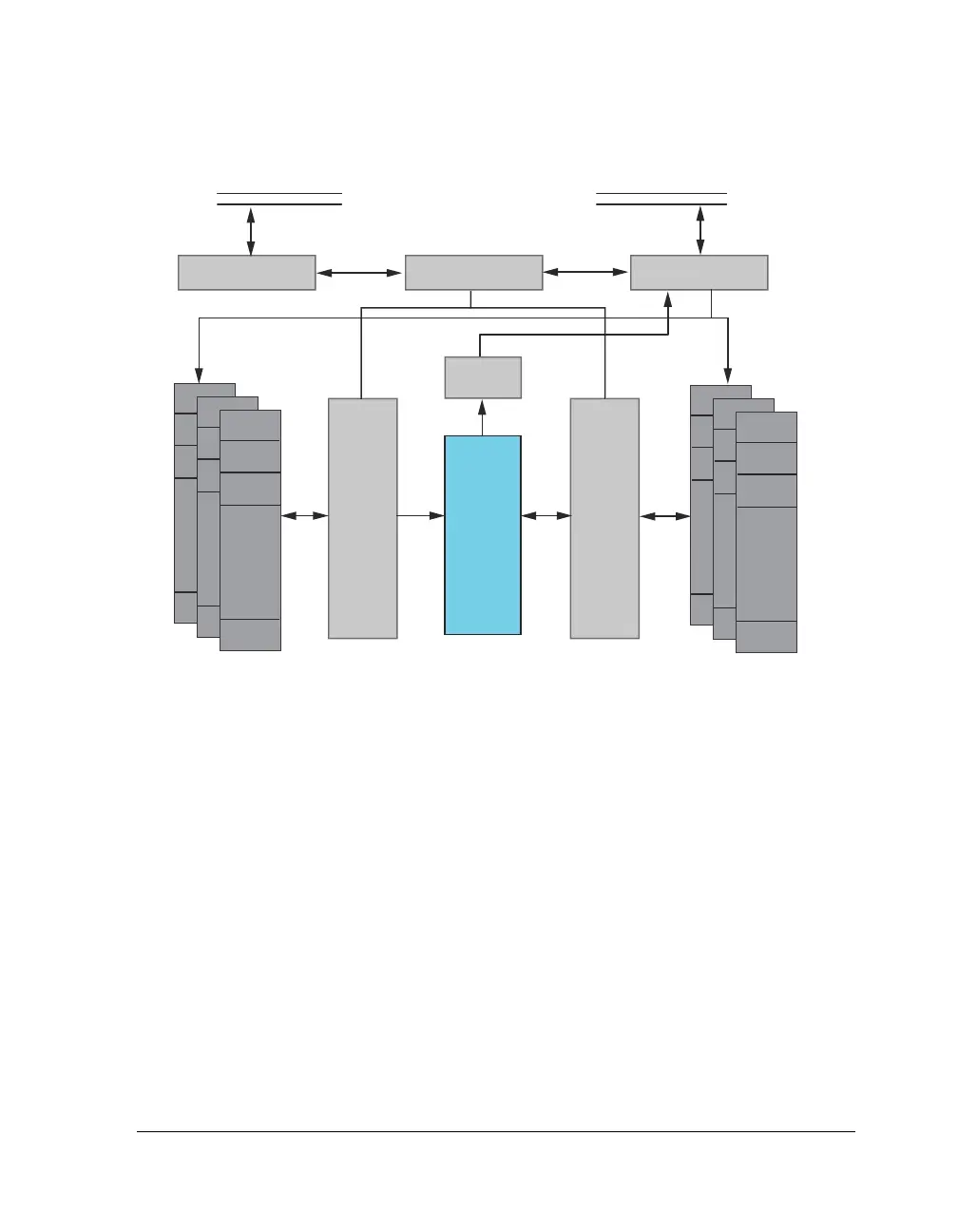

The IIR accelerator is implemented using Transposed Direct Form II

biquad which has less coefficient sensitivity. Figure 6-10 shows the signal

flow graph for the biquad structure.

Figure 6-9. IIR Accelerator Block Diagram

BIQUAD

BIQUAD

CORE PMD/DMD

BUS

IOD0

BUS

BIQUAD

COMPUTE

UNIT

(1 MAC)

RESULT

REGISTER

COEFF

ACCESS

CONTROL

DATA

AND

STATE

ACCESS

CONTROL

C

O

E

F

F

I

C

I

E

N

T

S

I

N

P

U

T

D

A

T

A

&

S

T

A

T

E

IIR CONTROL

REGISTERS

DMA

CONTROLLER

BIQUAD

STAGE 1

BIQUAD

STAGE 2

BIQUAD

STAGE N

BIQUAD

STAGE 3

.

.

.

BIQUAD

BIQUAD

BIQUAD

STAGE 1

BIQUAD

STAGE 2

BIQUAD

STAGE N

BIQUAD

STAGE 3

.

.

.

IIR CONTROLLER

Loading...

Loading...