Peripherals Routed Through the DPI

A-236 ADSP-214xx SHARC Processor Hardware Reference

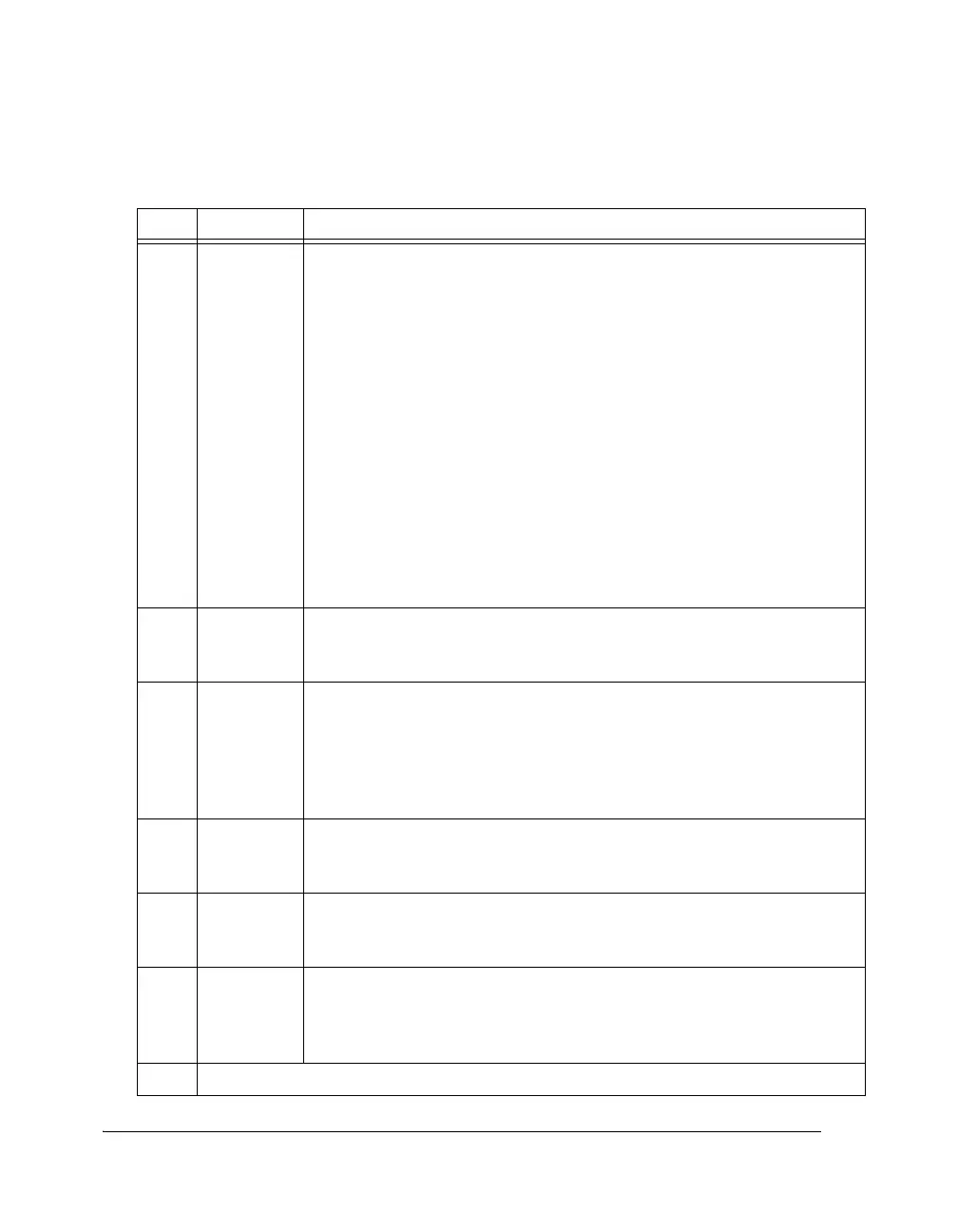

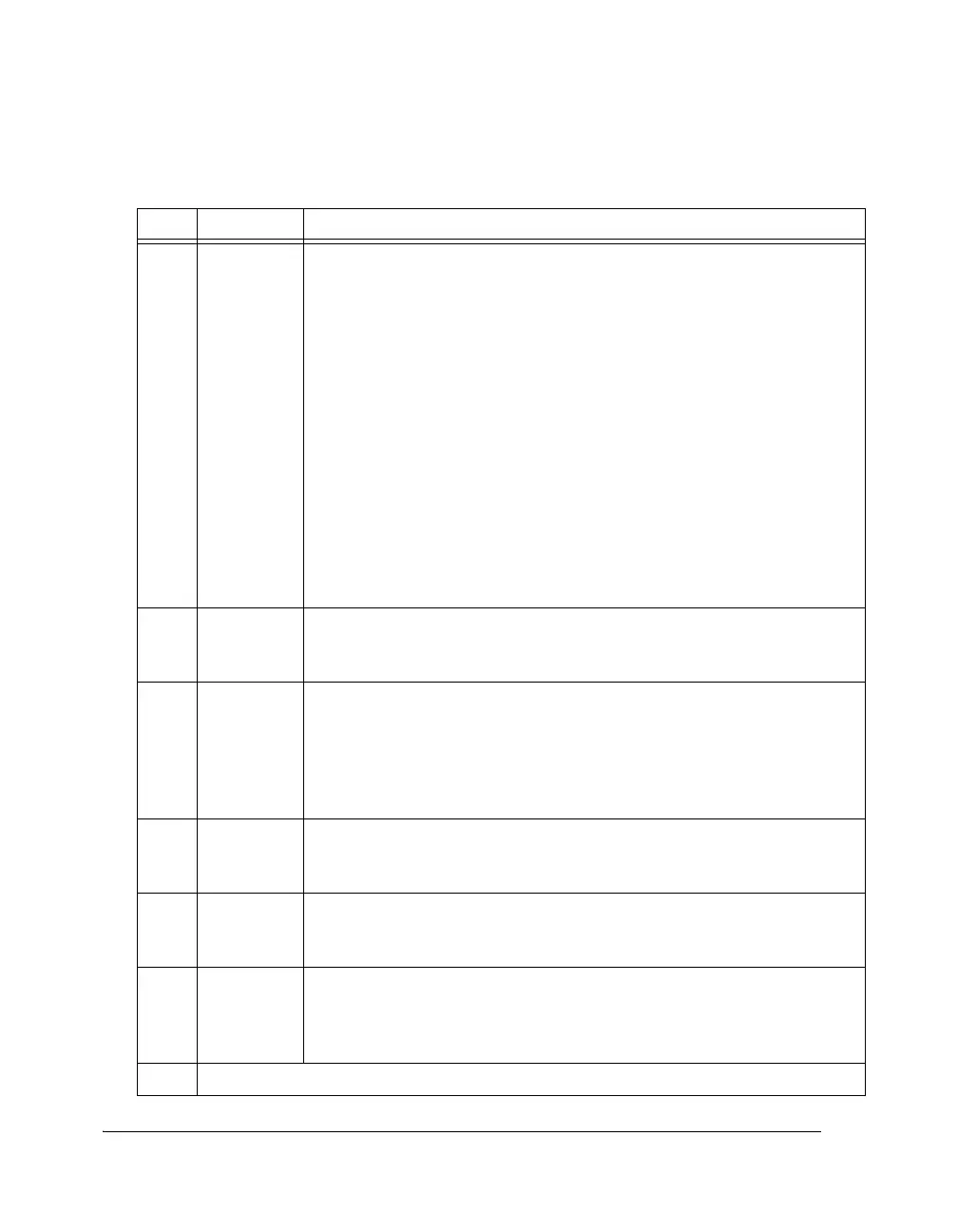

15 PACKEN Packing Enable. The SPI unpacks data when it transmits and packs data when

it receives. In order to communicate with 8-bit SPI devices and store 8-bit

words in internal memory, a packed transfer feature is built into the SPI port.

0 = No packing

1 = 8 to 16-bit packing

Note: This bit may be 1 only when WL = 00 (8-bit transfer). When in transmit

mode, the PACKEN bit unpacks data. When packing is enabled, two 8-bit

words are packed into one 32-bit word. When the SPI port is transmitting, two

8-bit words are unpacked from one 32-bit word. When receiving, words are

packed into one 32-bit word from two 8-bit words.

The value 0xXXLMXXJK (where XX is any random value and JK and LM are

data words to be transmitted out of the SPI port) is written to the TXSPI regis-

ter. The processor transmits 0xJK first and then transmits 0xLM.

The receiver packs the two words received, 0xJK and then 0xLM, into a

32-bit word. They appear in the RXSPI register as:

0x00LM00JK => if SGN is configured to 0 or L, J < 7

0xFFLMFFJK => if SGN is configured to 1 and L, J > 7

16 SGN Sign Extend.

0 = No sign extension

1 = Sign extension

17 SMLS Seamless Transfer.

0 = Seamless transfer disabled. After each word transfer there is a delay before

the next word transfer starts. The delay is 2.5 SPICLK cycles

1 = Seamless transfer enabled. There is no delay before the next word starts, a

seamless operation. Not supported in mode TIMOD1-0 = 00 and CPHASE=0

for all modes.

18 TXFLSH Flush Transmit Buffer. Write a 1 to clear TXSPI.

0 = TXSPI not cleared

1 = TXSPI cleared

19 RXFLSH Clear RXSPI. Write a 1 to clear RXSPI.

0 = RXSPI not cleared

1 = RXSPI cleared

20 ILPBK Internal Loop Back. This mode interconnects the MOSI with the MISO pins

internally. In this mode the SPIMS bit must be set.

0 = No internal loopback

1 = Internal loopback enabled

31–23 Reserved

Table A-122. SPICTL Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...