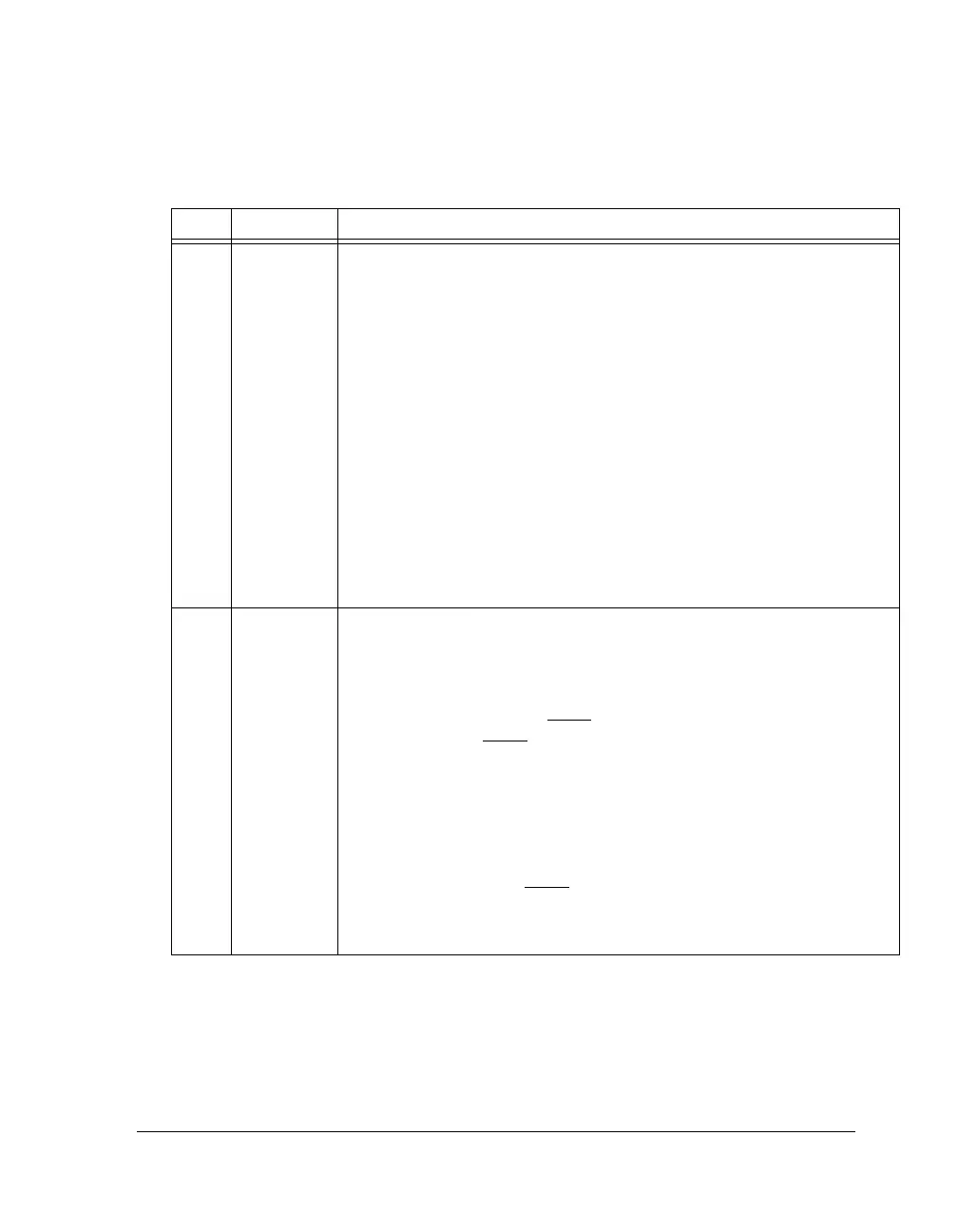

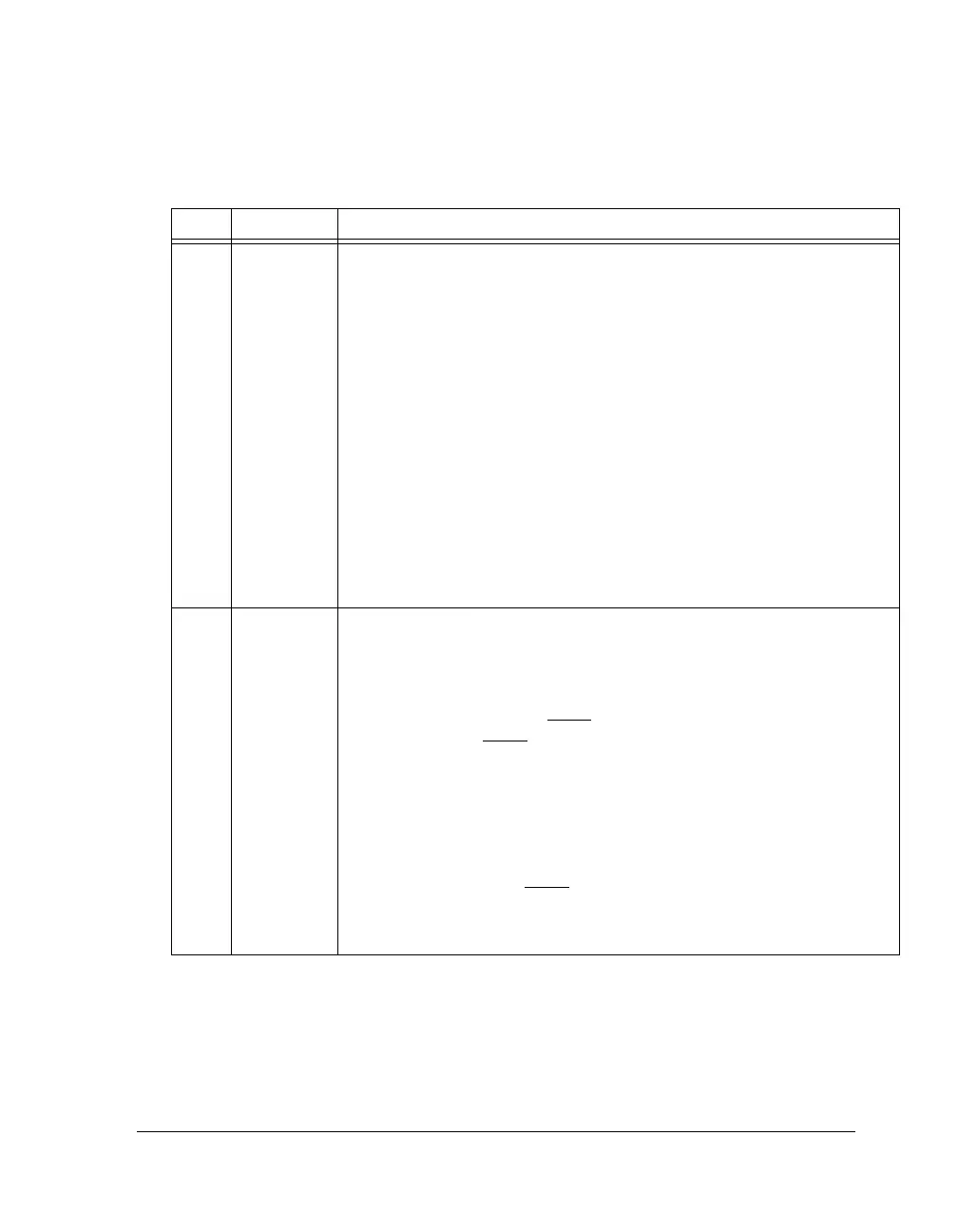

ADSP-214xx SHARC Processor Hardware Reference A-235

Registers Reference

13 OPD Open Drain Output Enable. Enables open drain data output enable for MOSI

and MISO pins.

0 = Drive (MOSI and MISO driven)

1 = Open drain (MOSI and MISO three-stated).

In a multimaster/slave SPI system, the data output pins (MOSI and MISO) can

be configured to behave as open drain drivers to prevent contention and possi-

ble damage to pin drivers. An external pull-up resistor is required on both the

MOSI/MISO pins when this option is selected.

When the OPD bit is set and the SPI ports are configured as masters,

the SPI_MOSI_O pin is three-stated. Instead the SPI_MOSI_PBEN_O pin is

driven and act as output enable pin. Note that the corresponding DPI input

buffer pin should be tied to GND.

Similarly, when OPD is set and the SPI ports are configured as slaves, the

SPI_MISO_O pin is three-stated. Instead the SPI_MISO_PBEN_O pin is

driven and act as output enable pin. Note that the corresponding DPI input

buffer pin should be tied to GND. See “Pin Buffers as Open Drain” on

page 9-11.

14 SPIEN SPI Port Enable. Enables the SPI port. If configured as a master (SPIMS=1)

and SPIEN=0, the MOSI and SPICLK outputs are disabled, and the MISO

input is ignored. If configured as a slave (SPIMS=0) and SPIEN=0, the MOSI

and SPICLK inputs are ignored, and the MISO output is disabled. The SPIEN

and SPIMS bits can be cleared by hardware if the MME-bit is set. For SPI

slaves, the slave-select input (

SPIDS) acts like a reset for the internal SPI logic.

For this reason, the SPIDS line must be error free.

The SPIEN bit can also be used as a software reset of the internal SPI logic. An

exception to this is the W1C-type (write 1-to-clear) bits in the SPISTATx regis-

ters. These bits remain set if they are already set.

Note: always clear the W1C-type bits in SPISTATx registers before re-enabling

the SPI, as these bits do not get cleared even if the SPI is disabled. This can be

done by writing 0xFF to the SPISTATx registers. In the case of an MME error,

enable the SPI ports after

SPIDS is deasserted.

0 = SPI module is disabled

1 = SPI module is enabled

Table A-122. SPICTL Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...