ADSP-2147x, ADSP-2148x External Port Registers

A-46 ADSP-214xx SHARC Processor Hardware Reference

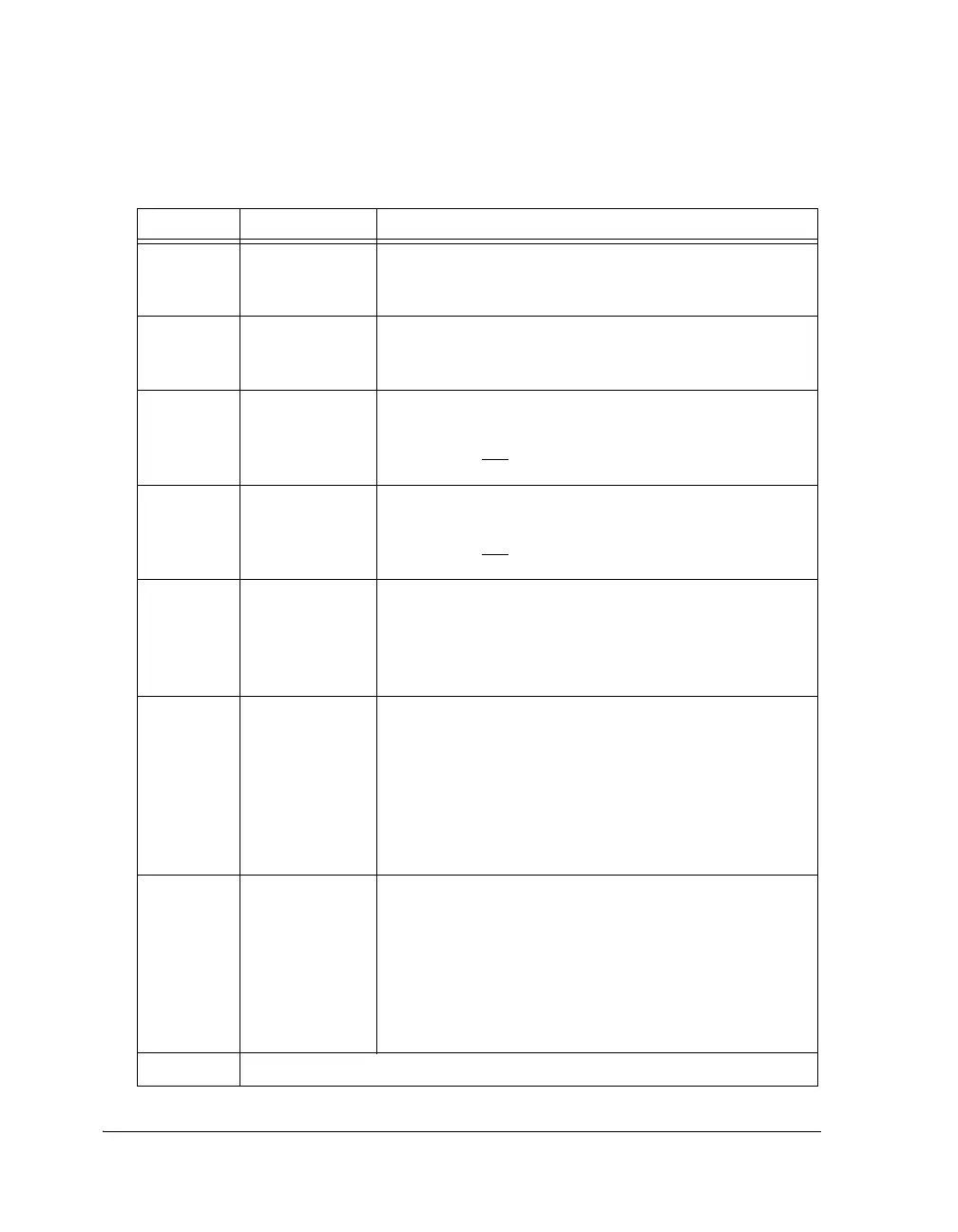

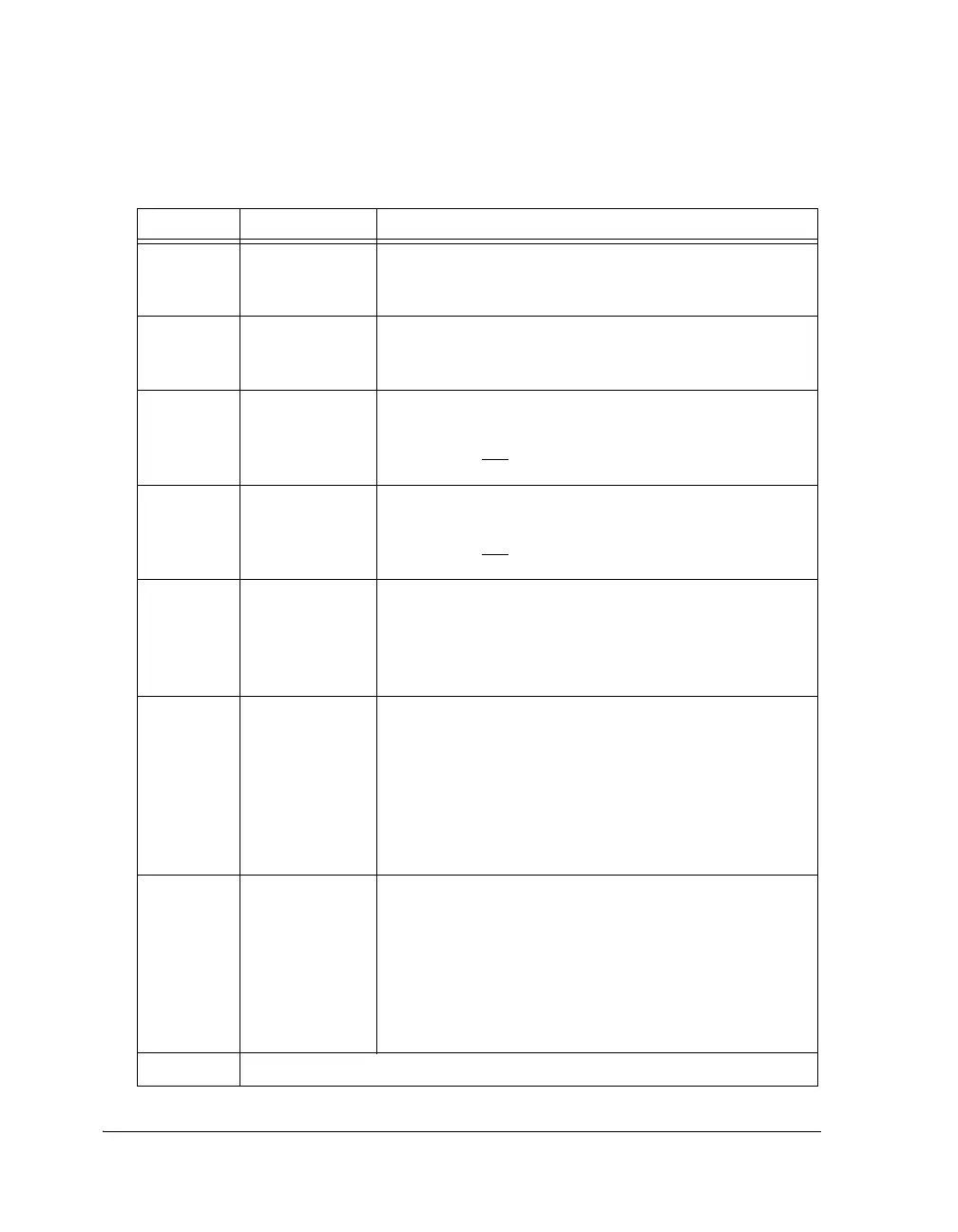

Table A-25. EPCTL Register Bit Descriptions (RW)

Bit Name Description

0B0SDSelect Bank 0 SDRAM.

0 = Bank 0 non-SDRAM

1 = Bank 0 SDRAM

1B1SDSelect Bank 1 SDRAM.

0 = Bank 1 Non-SDRAM

1 = Bank 1 SDRAM

2B2SDSelect Bank 2 SDRAM.

0 = Bank 2 Non-SDRAM

1 = Bank 2 SDRAM

Note that the

MS2 pin is multiplexed.

3B3SDSelect Bank 3 SDRAM.

0 = Bank 3 Non-SDRAM

1 = Bank 3 SDRAM

Note that the MS3 pin is multiplexed.

5–4 EPBR External Port Bus Priority.

00 = Reserved

01 = DMA has high priority

10 = Core has high priority

11 = Rotating priority (default)

7–6 DMAPR External Port Bus Priority.

00 = Priority order from highest to lowest is SPORT, external

port DMA, core

01 = Priority order from highest to lowest is external port

DMA, SPORT, core

10 = Highest priority is core. SPORT and external port DMA

are in rotating priority

11 = Rotating priority (default)

10–8 FRZDMA Arbitration Freezing Length for DMA.

000 = No Freezing

001 = 4 Accesses

010 = 8 Accesses

011 = 16 Accesses

100 = 32 Accesses

101 = Page size (SDRAM only1)

110, 111 = Reserved

11 Reserved

Loading...

Loading...