ADSP-214xx SHARC Processor Hardware Reference 3-113

External Port

these delay line reads. Once the read count completes, the

ICEP

register decrements to zero (both ICEP and TCEP are zero) for the

final tap. Finally, the delay line DMA access completes and the

DMA completion interrupt is generated. If chaining is enabled, the

interrupt is dependent on the

PCI bit setting. The delay line DMA

can only be initialized using the TCB. In order to use the delay line

DMA for a single DMA sequence, initialize the CPEP register to

zero in the TCB.

For each 32-bit tap read, the external read index is shown in Table 3-27.

Note that one tap list entry starts multiple reads.

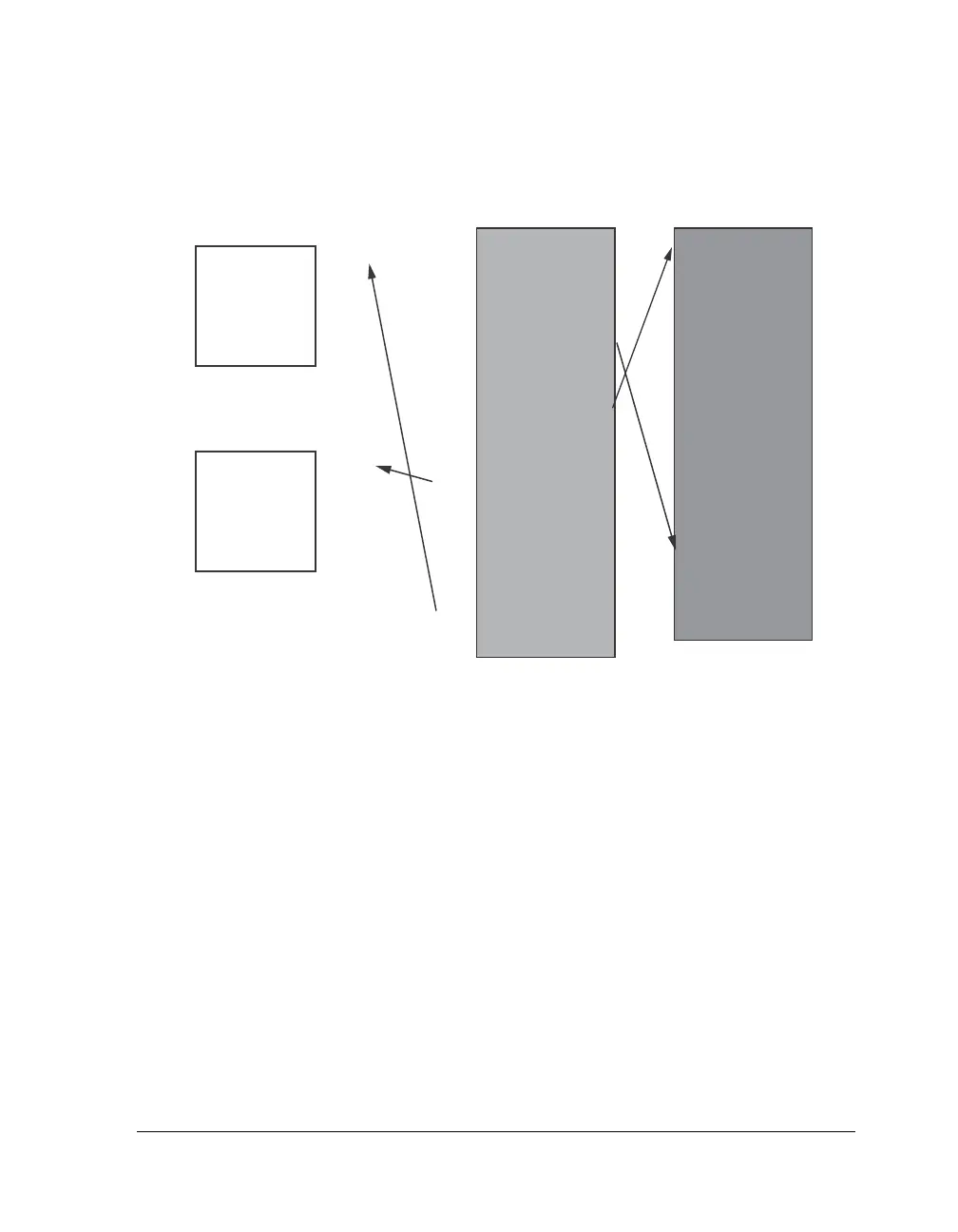

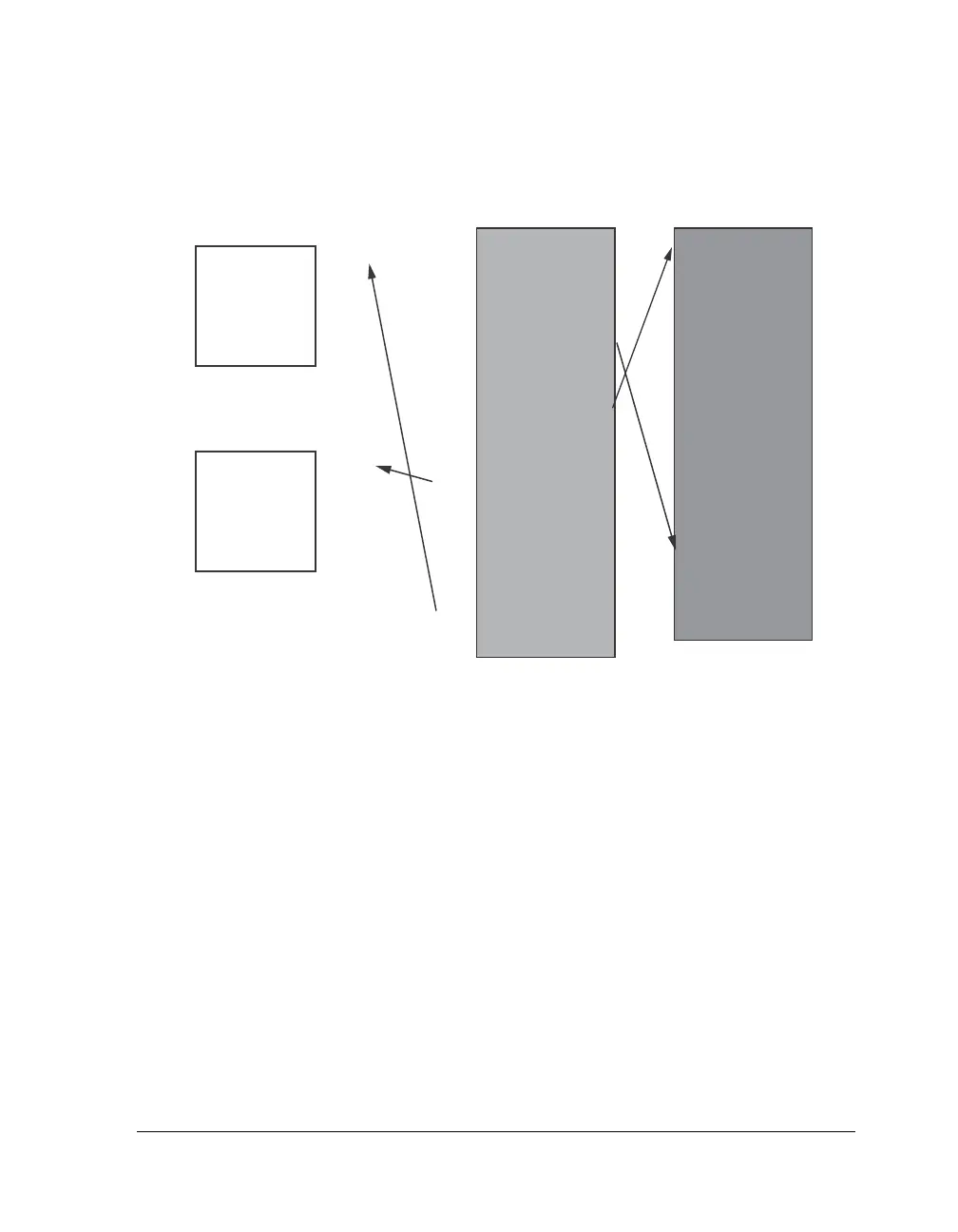

Figure 3-28. Delay Line DMA Reads

IIEP

IMEP

ICEP

EIEP

EMEP

EBEP

ELEP

RIEP

RCEP

RMEP

TCEP

TPEP

CPEP

0xC2000

1

100

0x0009

1

0x00000

256

0xC1000

1

1

3

0xC0000

---

0xAAAAAA

0xBBBBBB

0xCCCCCC

0xDDDDDD

0xEEEEEE

0xFFFFFF

0x121212

0x343434

0x565656

0x787878

. . .

?

0

0

0

0

0

0

0

0

0

0

.

0

DELAY-LINE

TAP LIS

T

SAMPLE (N

-

M)

INTERNAL MEMORY

DMA DESTINATION

(SAMPLES FETCHED

FROM D-LINE)

EXTERNAL MEMORY

(DELAY LINE)

0

xC000

0

xC001

0

xC002

0

xC000

0

xC001

0

xC002

....

-2

-5

-7

....

0x343434

0XEEEEEE

0XCCCCCC

....

....

Loading...

Loading...