ADSP-214xx SHARC Processor Hardware Reference A-259

Registers Reference

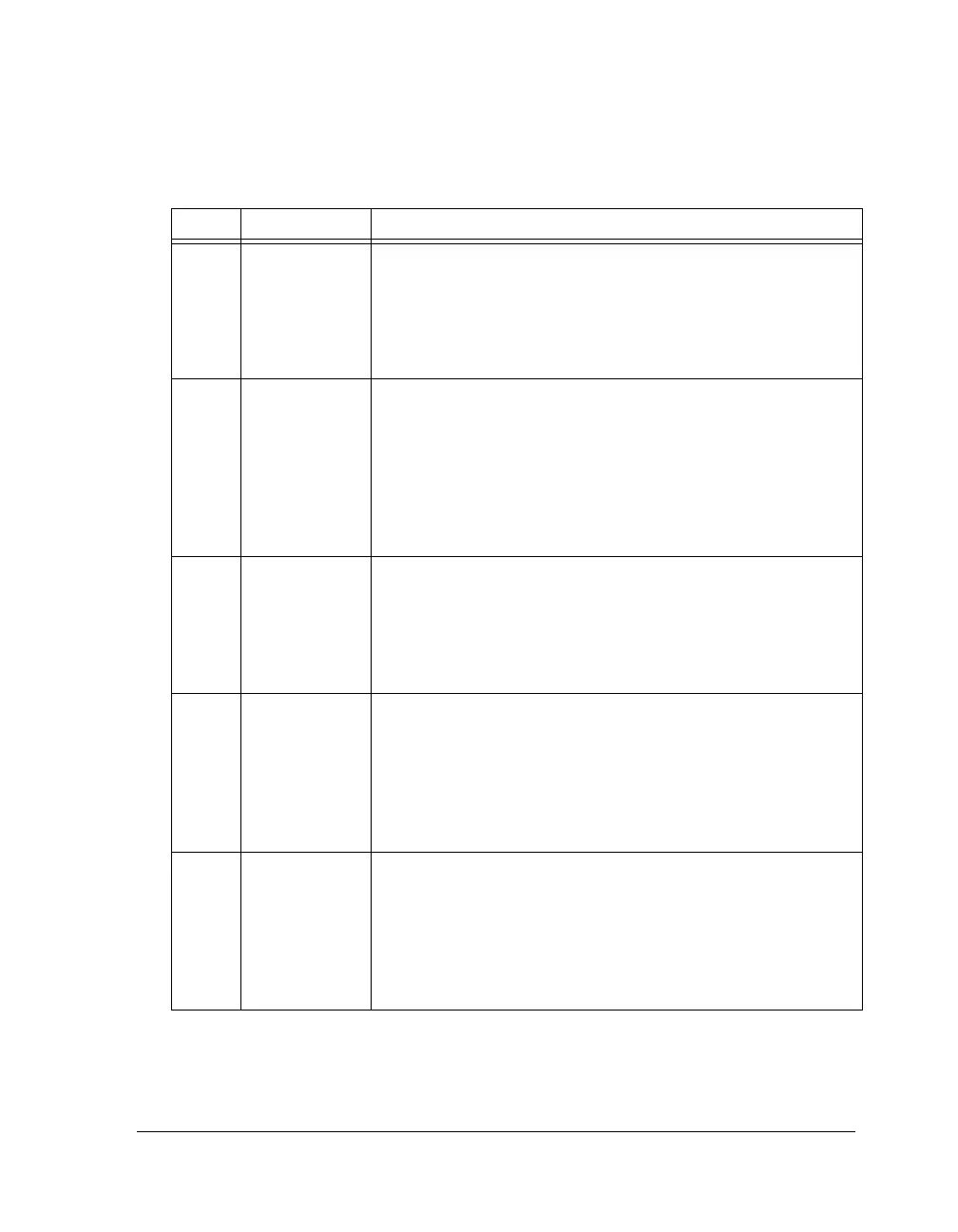

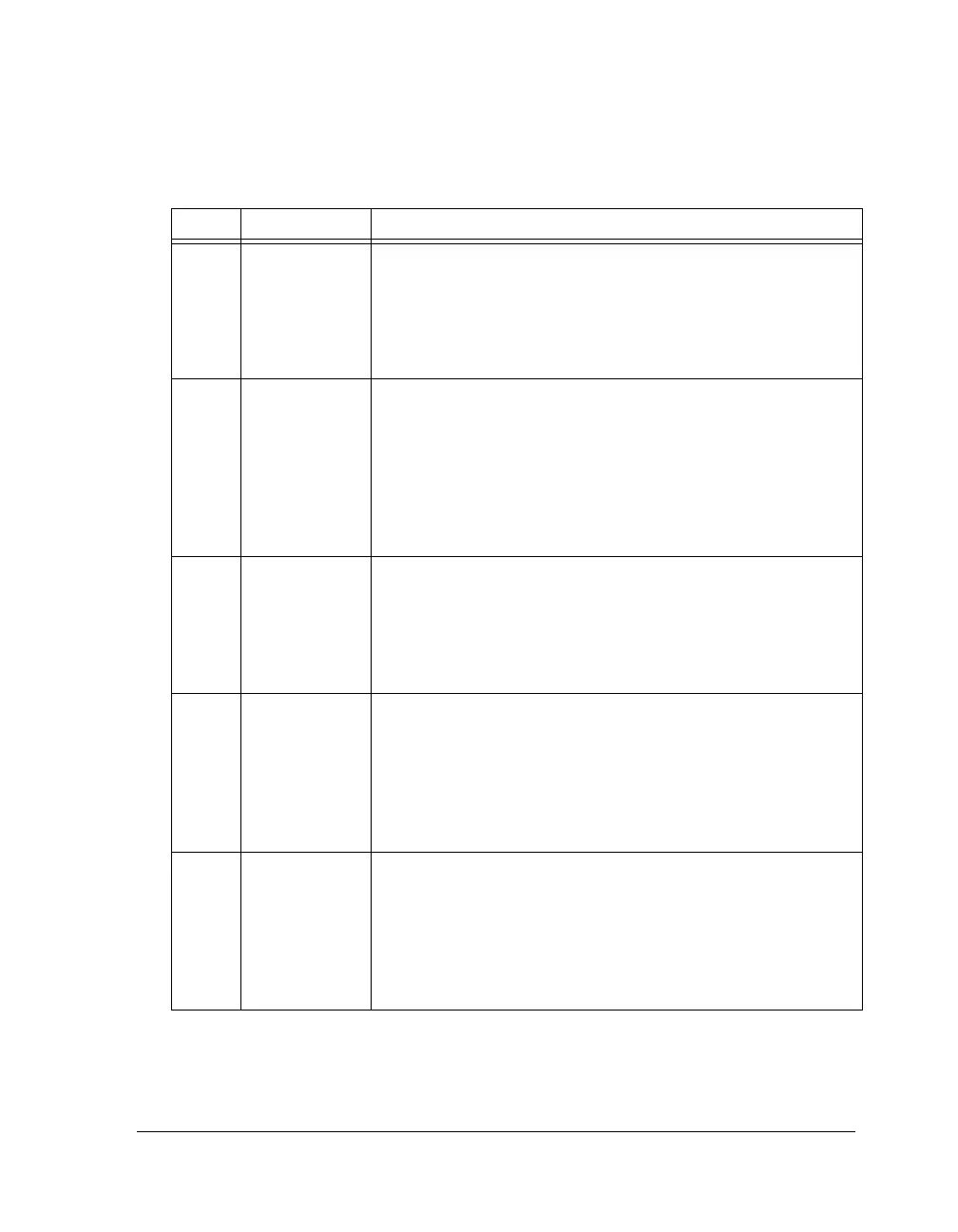

4TWISTOP Issue STOP Condition.

0 = Normal transfer operation

1 = The transfer concludes as soon as possible avoiding any error con-

ditions (as if data transfer count had been reached) and at that time

the interrupt source register is updated along with any associated sta-

tus bits.

5TWIRSTART Repeat START.

0 = Transfer concludes with a STOP condition

1 = Issue a repeat START condition at the conclusion of the current

transfer (DCNT = 0) and begin the next transfer. The current trans-

fer is concluded with updates to the appropriate status and interrupt

bits. If errors occurred during the previous transfer, a repeat START

does not occur. In the absence of any errors, master enable (MEN)

does not clear itself on a repeat start.

13–6 TWIDCNT Data Transfer Count. Indicates the number of data bytes to transfer.

As each data word is transferred, the data transfer count is decre-

mented. When DCNT is zero, a STOP (or restart condition) is

issued. Setting DCNT to 0xFF disables the counter. In this transfer

mode, data continues to be transferred until it is concluded by setting

the STOP bit.

14 TWISDAOVR Serial Data (TWI_DATA) Override. For use when direct control of

the Serial Data line is required. Normal master and slave mode opera-

tion should not require override operation.

0 = Normal serial data operation under the control of the transmit

shift register and acknowledge logic

1 = Serial data output is driven to an active “zero” level, overriding all

other logic. This state is held until the bit location is cleared.

15 TWISCLOVR Serial Clock (TWI_Clock) Override. For use when direct control of

the serial clock line is required. Normal master and slave mode opera-

tion should not require override operation.

0 = Normal serial clock operation under the control of master mode

clock generation and slave mode clock stretching logic

1 = Serial clock output is driven to an active “zero” level, overriding

all other logic. This state is held until the bit location is cleared.

Table A-140. TWIMCTL Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...