ADSP-214xx SHARC Processor Hardware Reference 2-31

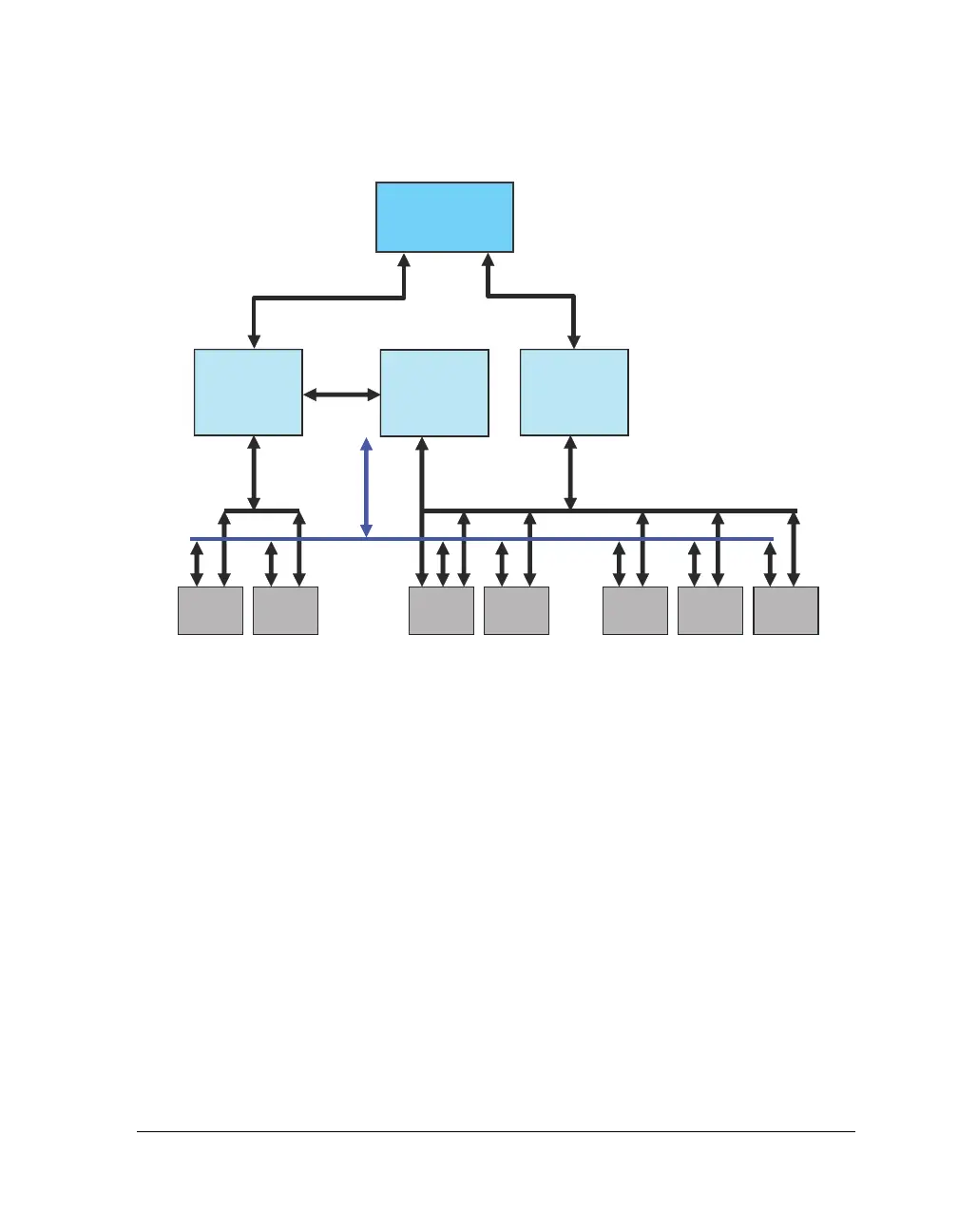

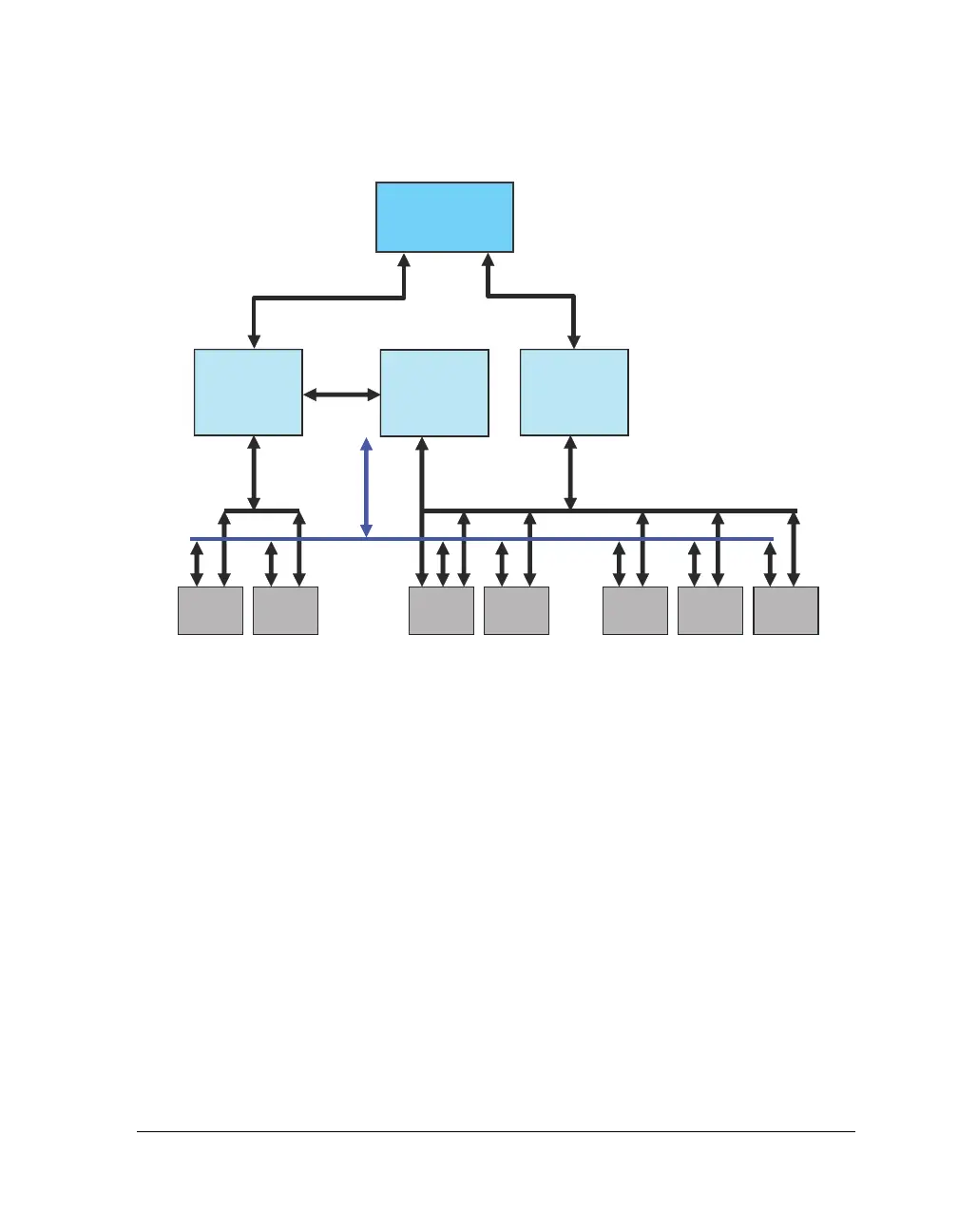

I/O Processor

The IOD0 and IOD1 buses operate independently. However, in

some cases there may be address conflicts if both buses access the

same internal memory block. In this case, the IOD0 bus has first

priority.

Each I/O port has one or more DMA channels, and each channel has a

single request and a single grant. When a particular channel needs to read

or write data to internal memory, the channel asserts an internal DMA

request. The I/O processor prioritizes the request with all other valid

DMA requests. When a channel becomes the highest priority requester,

the I/O processor asserts the channel’s internal DMA grant. In the next

clock cycle, the DMA transfer starts. Table 2-28 on page 2-36 shows the

paths for internal DMA requests within the I/O processor.

Figure 2-2. I/O Processor Bus Structure

EXTERNAL

PORT ARBITER

IOD1

PERIPHERAL

ARBITER

IOD0

INTERNAL

MEMORY I/F

ARBITER

IOD1 BUS

IOD0 BUS

...

SPORTxAMI

DDR2

or

SDRAM

SPI

HW

ACC

LINK

PORT

UART

I/O SPEP

BUS

SPORT EP

(SPEP) ARBITER

PERIPHERAL DMA BUS

EXTERNAL PORT

DMA BUS

CORE BUS

CORE BUS

Loading...

Loading...