ADSP-214xx SHARC Processor Hardware Reference 7-11

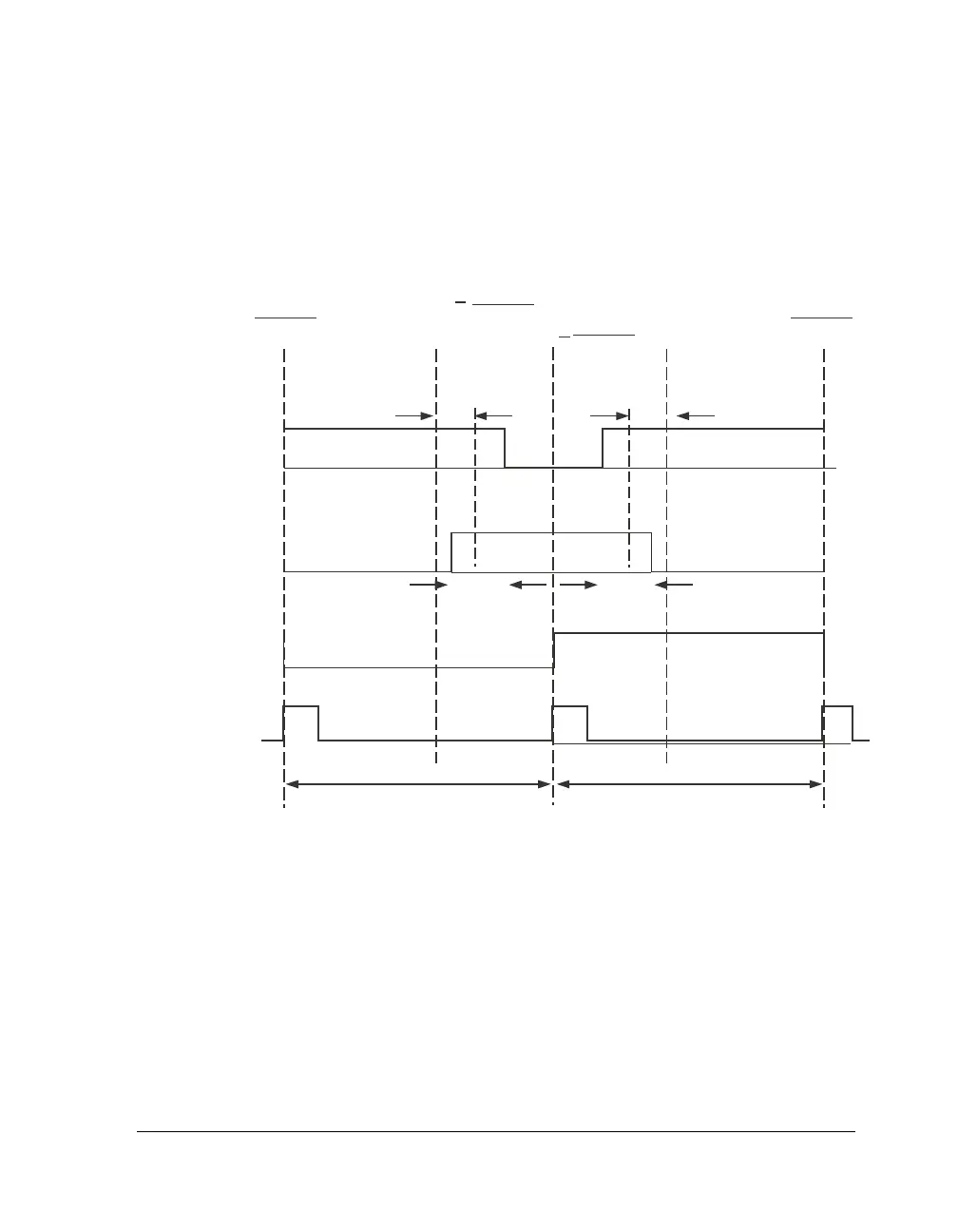

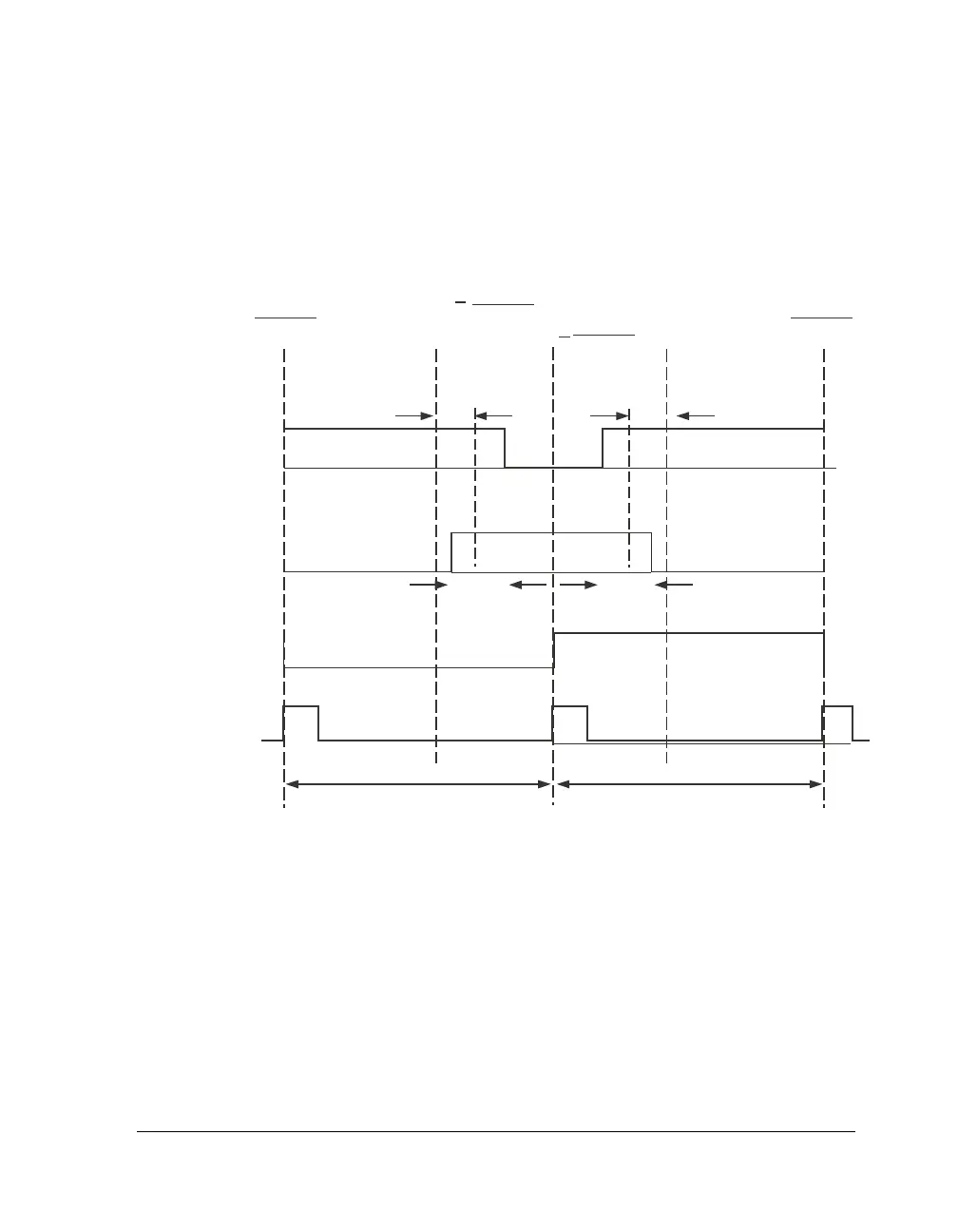

Pulse Width Modulation

where subscript 1 refers to the value of that register during the first half

cycle and subscript 2 refers to the value during the second half cycle. The

corresponding duty cycles are:

Figure 7-3. Center-Aligned Paired PWM in Double Update Mode,

Low Polarity

T

AH

PWMPERIOD

1

2

-----------------------------------------

PWMPERIOD

2

2

-----------------------------------------

PWMCHA

1

PWMCHA

2

PWMDT

1

PWMDT

2

––+++

t

PCLK

×=

......................

.....

......................

.....

PWMTM

1

PWMTM

2

PWMCHA

1

PWMCHA

2

PWMTM

1

2

+

0

PWMTM

1

2

PWMTM

2

2

+

0

2xPWMDT

1

2xPWMDT

2

count

pwm_ah

pwm_al

PWMTM

2

2

PWM INTERRUPT

LATCH BIT

PWM PHASE BIT

d

AL

T

AL

T

S

-----------

1

2

---

PWMCHA

1

PWMCHA

2

PWMDT

1

PWMDT

2

+++()

PWMPERIOD

1

PWMPERIOD

2

+()

-------------------------------------------------------------------------------------------------------------------------------------------

–==

Loading...

Loading...