Interrupts

10-52 ADSP-214xx SHARC Processor Hardware Reference

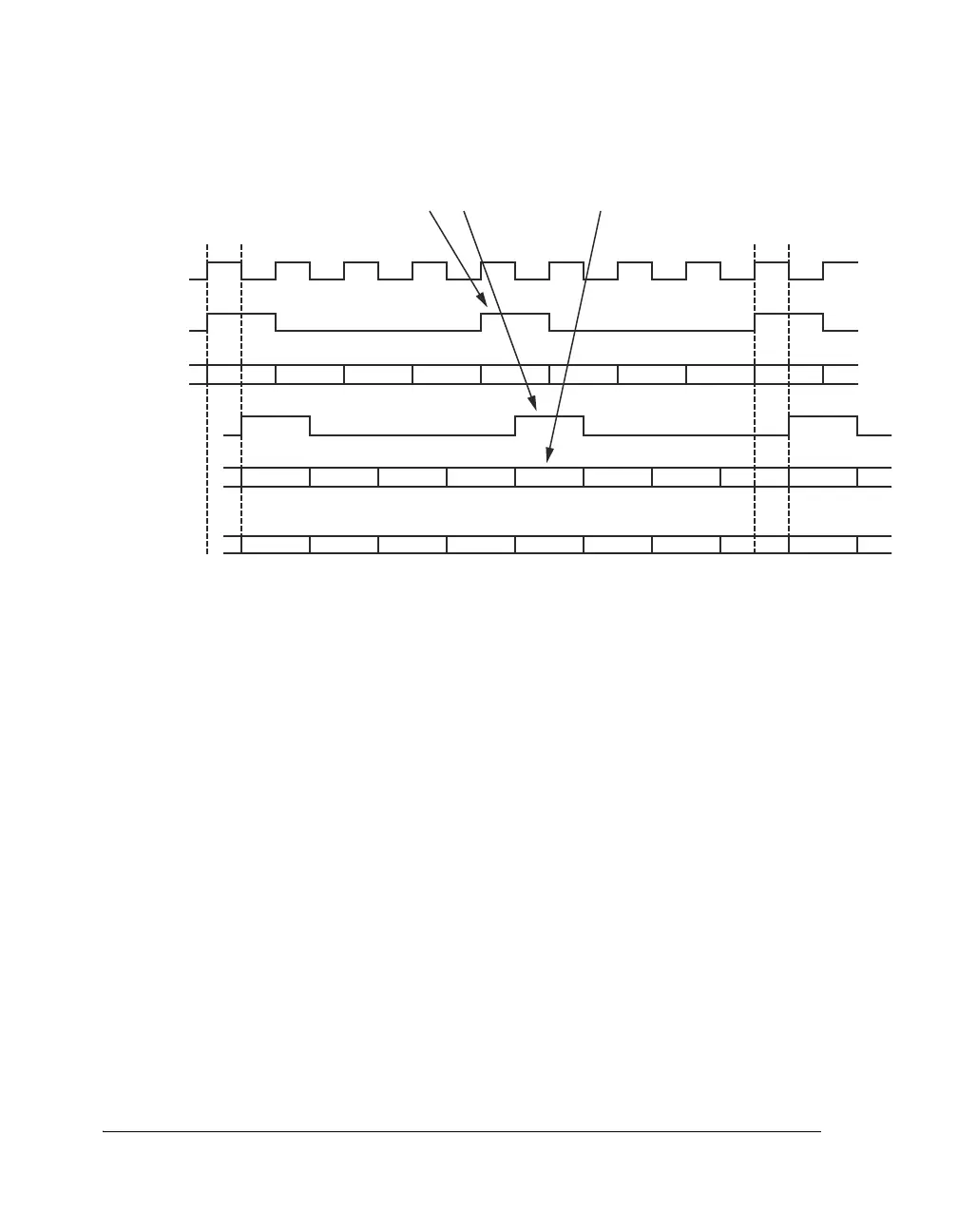

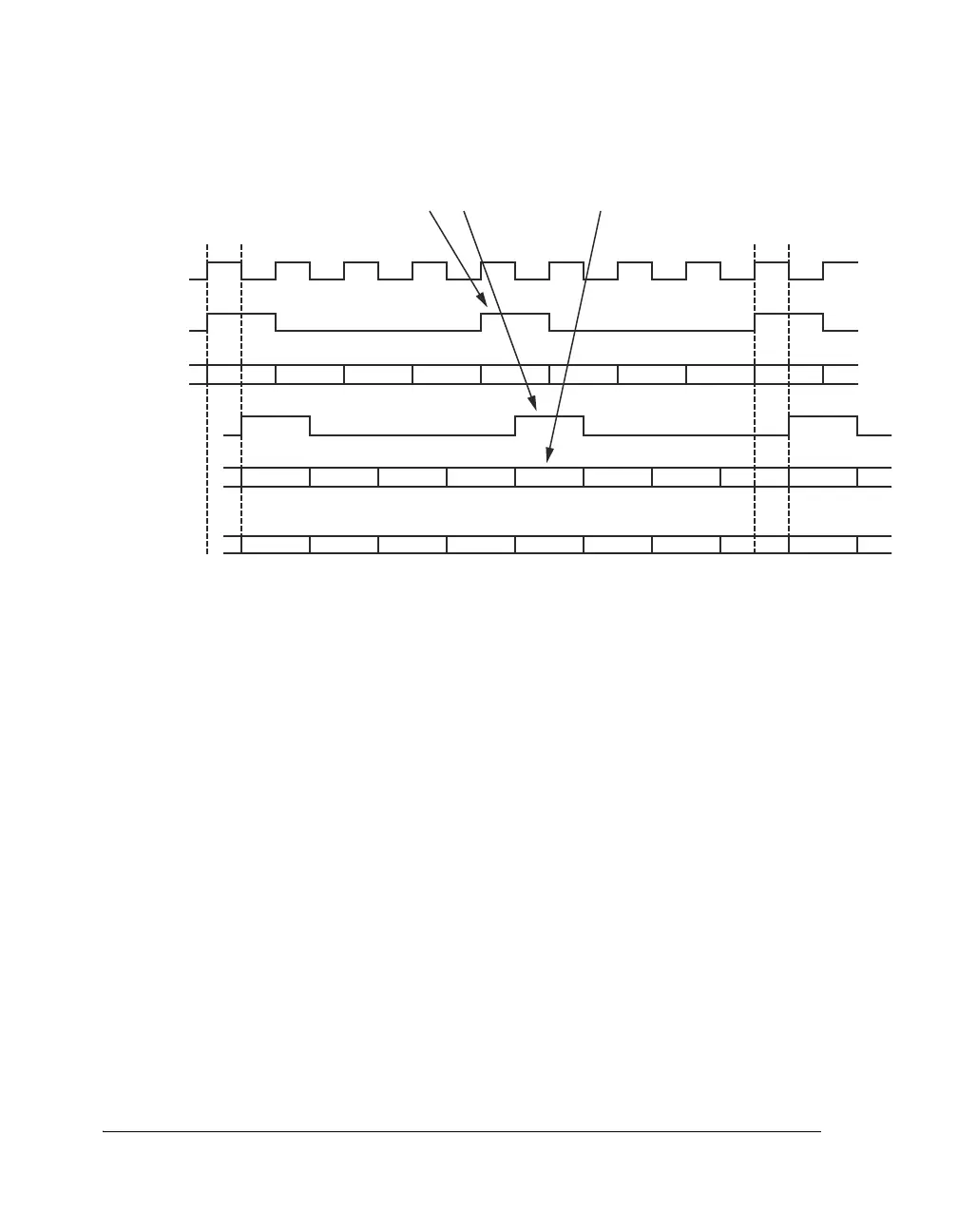

When a serial port is receiving or transmitting, its bit count is set to a

word length (for example 32 bits). After each clock edge the bit count is

decremented. After the word is received/transmitted the bit count reaches

zero, and on next frame sync it is set to 32. When active transmission or

reception is occurring, the bit count value is non-zero. When a frame sync

with a bit count of non-zero is detected, a frame sync error occurs.

Note that a frame sync error is not detected in following cases.

• When there is no active data transmit/receive and the frame sync

pulse occurs due to noise in the input signal. This is considered a

valid frame sync.

• If there is a underflow or overflow error. SPORT error logic does

not run (the bit count is not set and decremented) if there is an

underflow error. Therefore, frame sync errors can not be detected.

Figure 10-10. Frame Sync Error Detection

DRIVE

SCLK

SDRIVE

DATA

DRIVE

FS

D7 D6 D5 D4 D3 D2 D1 D0

76543210

D7 D6 D5 D4 D3 D2 D1 D0

SAMPLED

FS

SAMPLED

DATA

SLEN

COUNTER

ERRONEOUS

EARLY FS

SLEN COUNTER NOT ZERO

=> SPERRI INTERRUPT

Loading...

Loading...