Peripheral Registers

A-80 ADSP-214xx SHARC Processor Hardware Reference

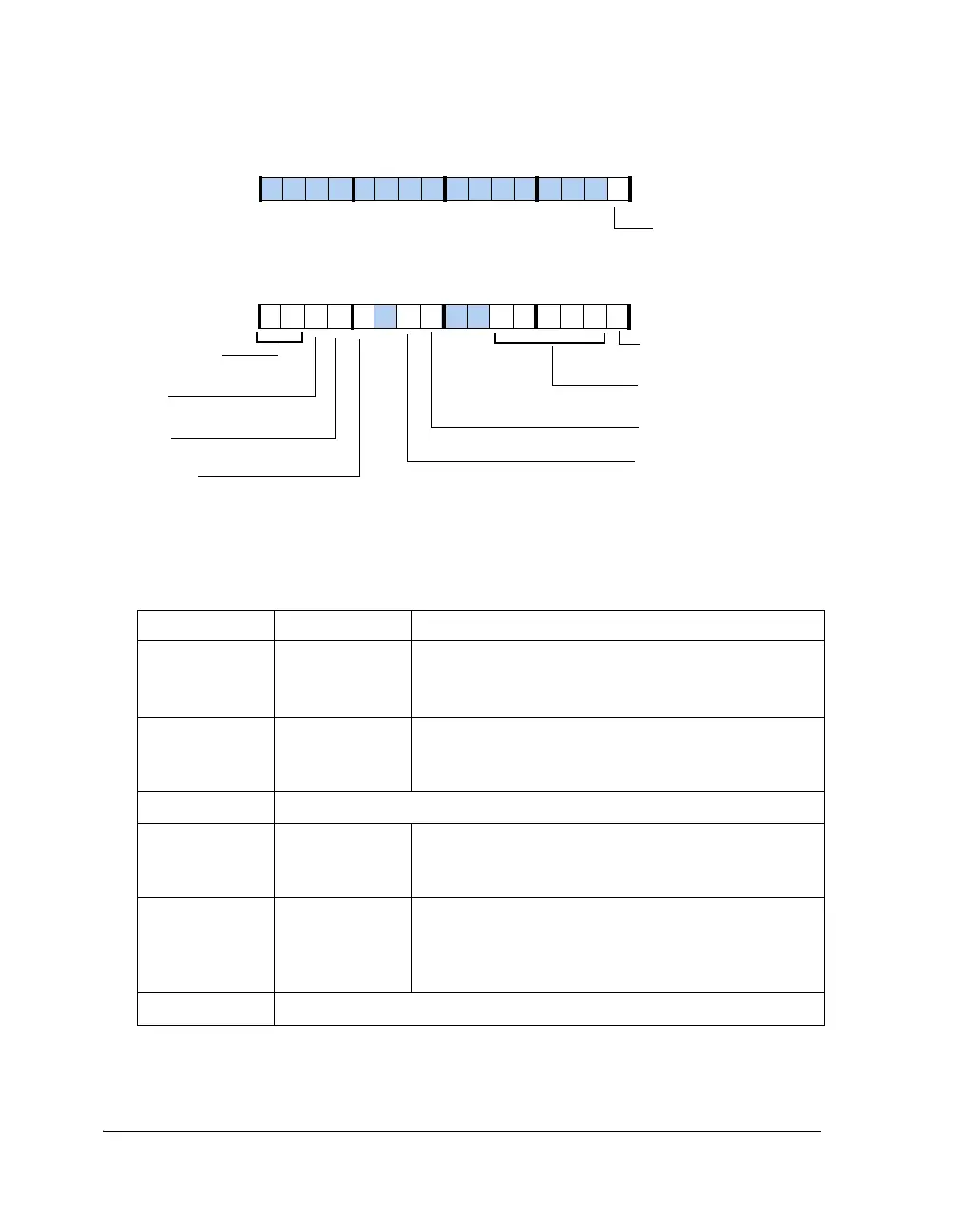

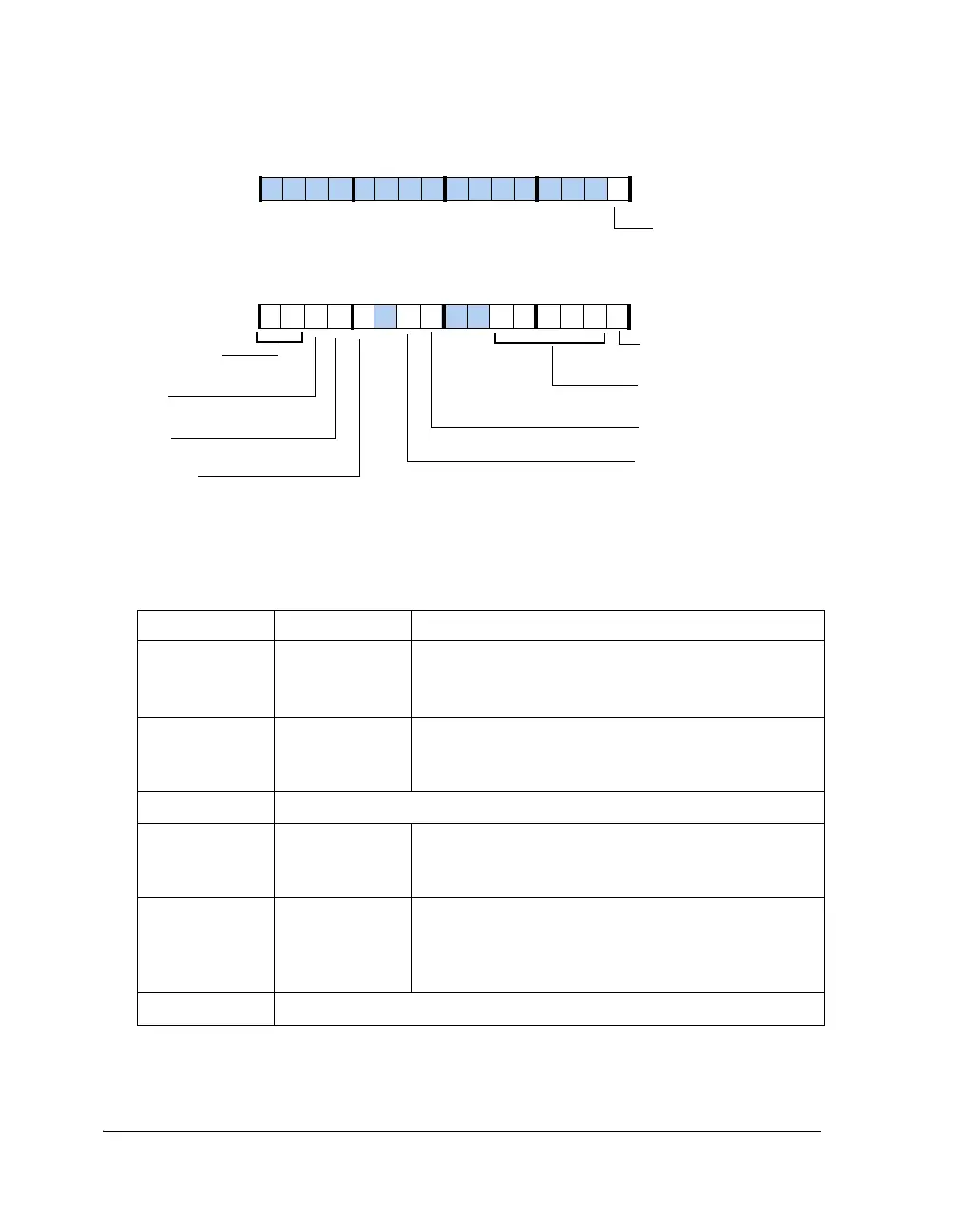

Figure A-35. FIRCTL1 Register

Table A-47. FIRCTL1 Register Bit Descriptions (RW)

Bits Name Description

0FIR_ENFIR Enable.

0 = FIR disabled

1 = FIR enabled

5–1 FIR_CH32–1 Number of Channels. Programmable between 0–31

0 = FIR_CH1

31 = FIR_CH32

7–6 Reserved

8 FIR_DMAEN DMA Enable.

0 = DMA disabled

1 = DMA enabled

9FIR_CAIChannel Auto Iterate.

0 = Processing stops once all channels are over

1 = Moves to first channel and continues processing in a

loop when all channels are over

10 Reserved

FIR_TC

Two’s-Complement Format

FIR_EN

FIR_CH (5–1)

Number of Channels

Accelerator Enable

FIR_DMAEN

DMA Enable

FIR_FXD

Fixed-point Accelerator Select

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

FIR_RND (16–14)

Rounding Mode

FIR_RND (16–14)

Rounding Mode Select

For Floating-point Mode

FIR_CCINTR

Channel Complete Interrupt

FIR_CAI

Channel Auto Iterate

Loading...

Loading...