ADSP-214xx SHARC Processor Hardware Reference A-233

Registers Reference

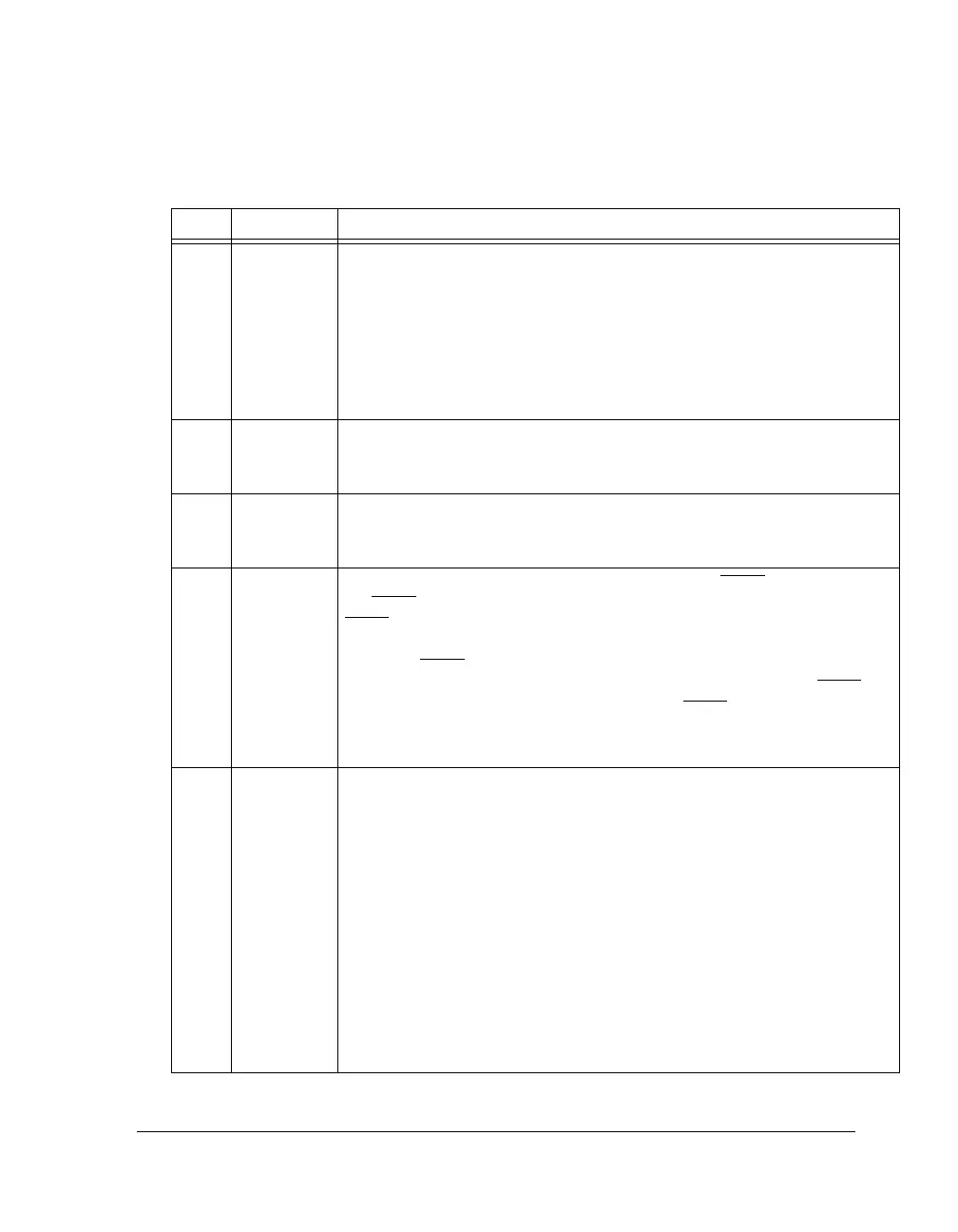

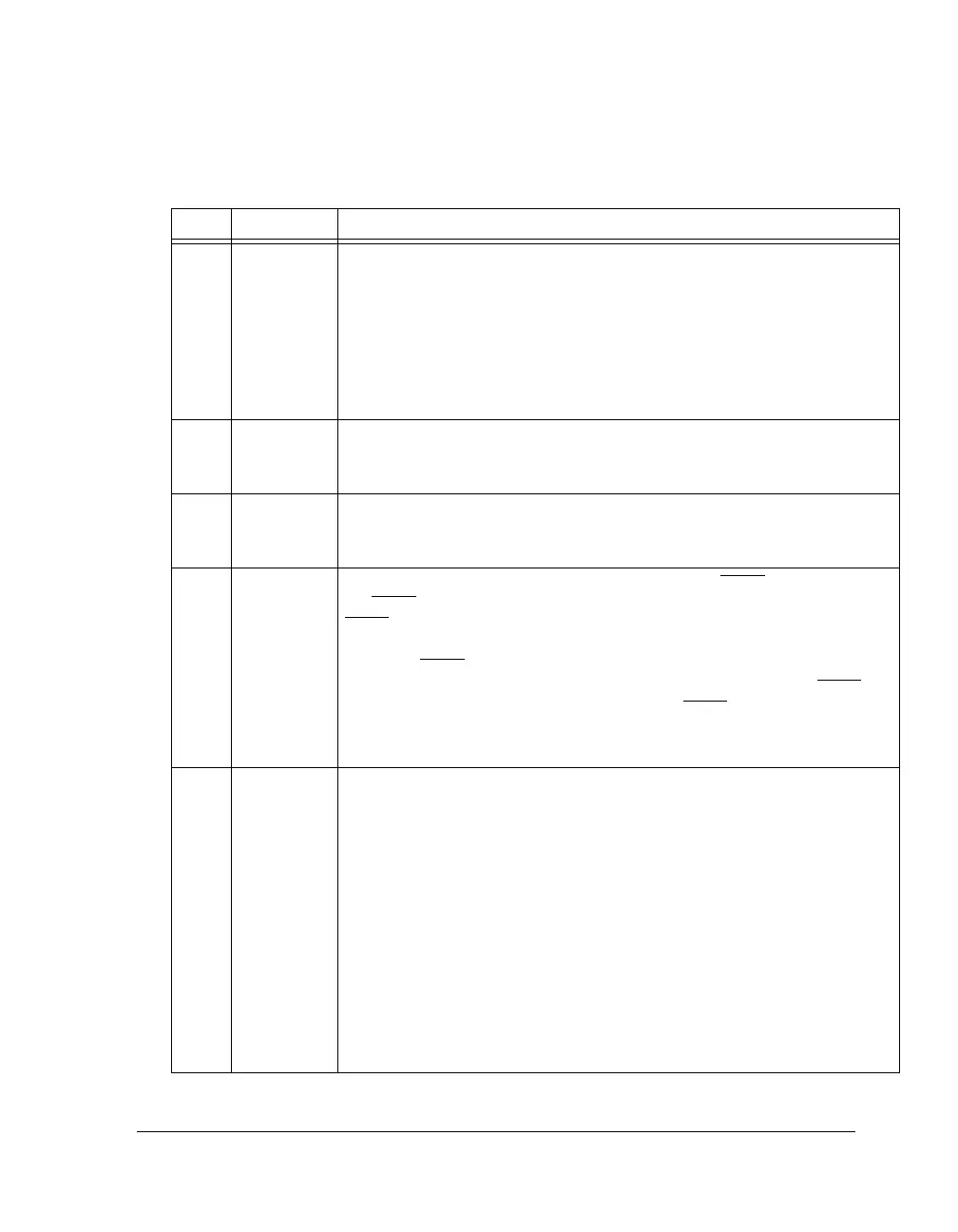

Table A-122. SPICTL Register Bit Descriptions (RW)

Bit Name Description

1–0 TIMOD Transfer Initiation Mode. Defines transfer initiation mode and interrupt gener-

ation.

00 = Initiate transfer by read of receive buffer. Interrupt active when receive

buffer is full.

01 = Initiate transfer by write to transmit buffer. Interrupt active when transmit

buffer is empty.

10 = Enable DMA transfer mode. Interrupt configured by DMA.

11 = Reserved

2SENDZSend Zero. Send zero or the last word when TXSPI is empty.

0 = Send last word

1 = Send zeros

3GM Get Data. When RXSPI is full, get data or discard incoming data.

0 = Discard incoming data

1 = Get more data, overwrites the previous data

4ISSEN Input Slave-Select Enable. Enables slave-select input (

SPIDS pin) for the mas-

ter. SPIDS operation depends on the SPI configuration. If the SPI is a slave,

SPIDS acts as the slave-select input. The state of this input pin is observable in

bit 7 of the SPIFLGx register.

As master, SPIDS can serve as an error-detection input in a multimaster envi-

ronment. The ISSEN-bit enables this feature. When ISSEN =1, the

SPIDS

input is the master mode error input; otherwise, SPIDS is ignored.

0 = Disable

1 = Enable

5DMISODisable MISO Pin. Disables MISO as an output. This is needed in an environ-

ment where a master wishes to transmit to various slaves at one time (broad-

cast). However, only one slave is allowed to transmit data back to the master.

This bit should be set for all slaves, except the one from whom the master

wishes to receive data.

Different CPUs or processors can take turns being master, and one master may

simultaneously shift data into multiple slaves (broadcast mode).

However, only one slave may drive its output to write data back to the

master at any given time. This must be enforced in the broadcast mode, where

several slaves can be selected to receive data from the master, but only one slave

can be enabled to send data back to the master. The (DMISO) bit disables

MISO as an output.

0 = MISO enabled

1 = MISO disabled

Loading...

Loading...