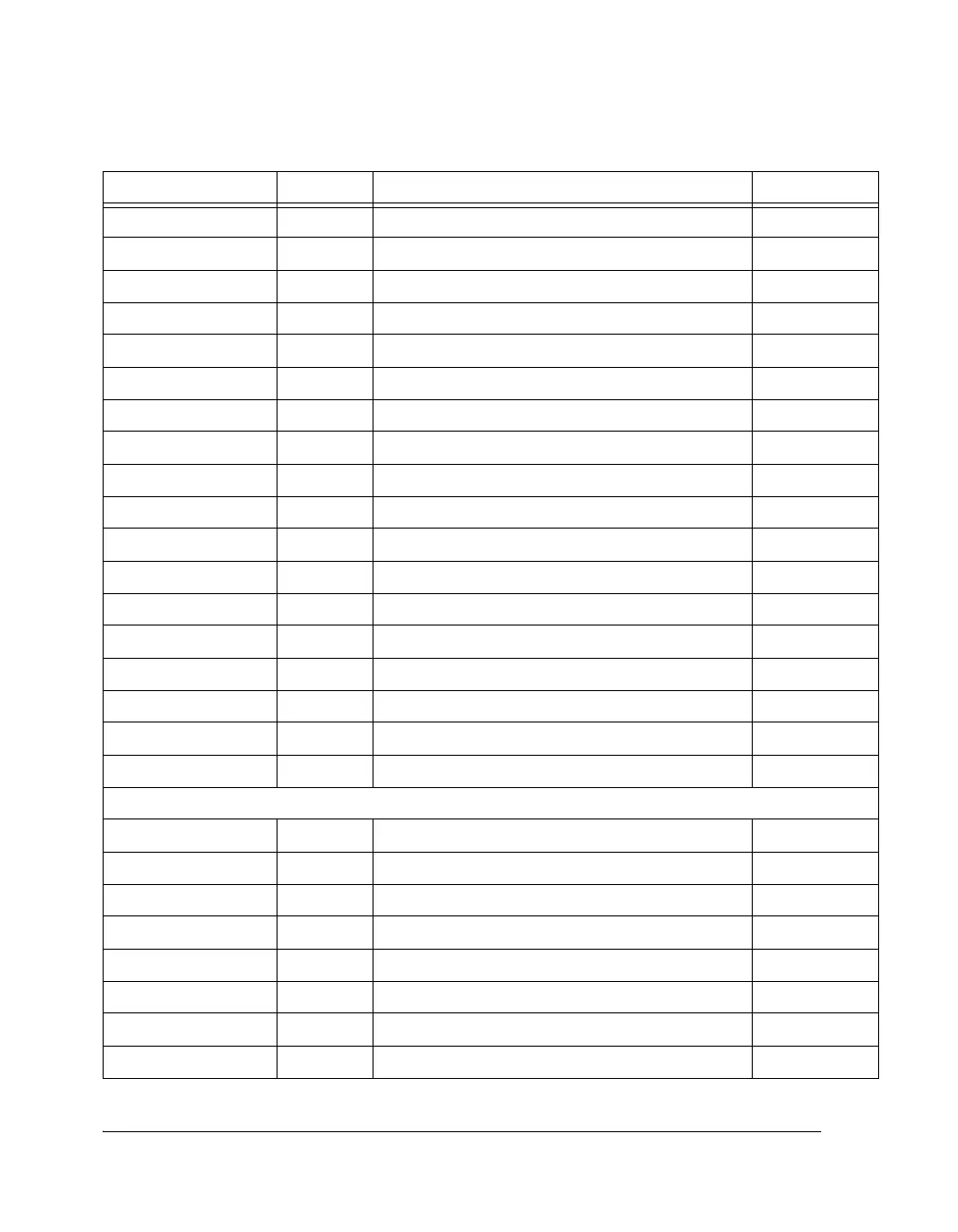

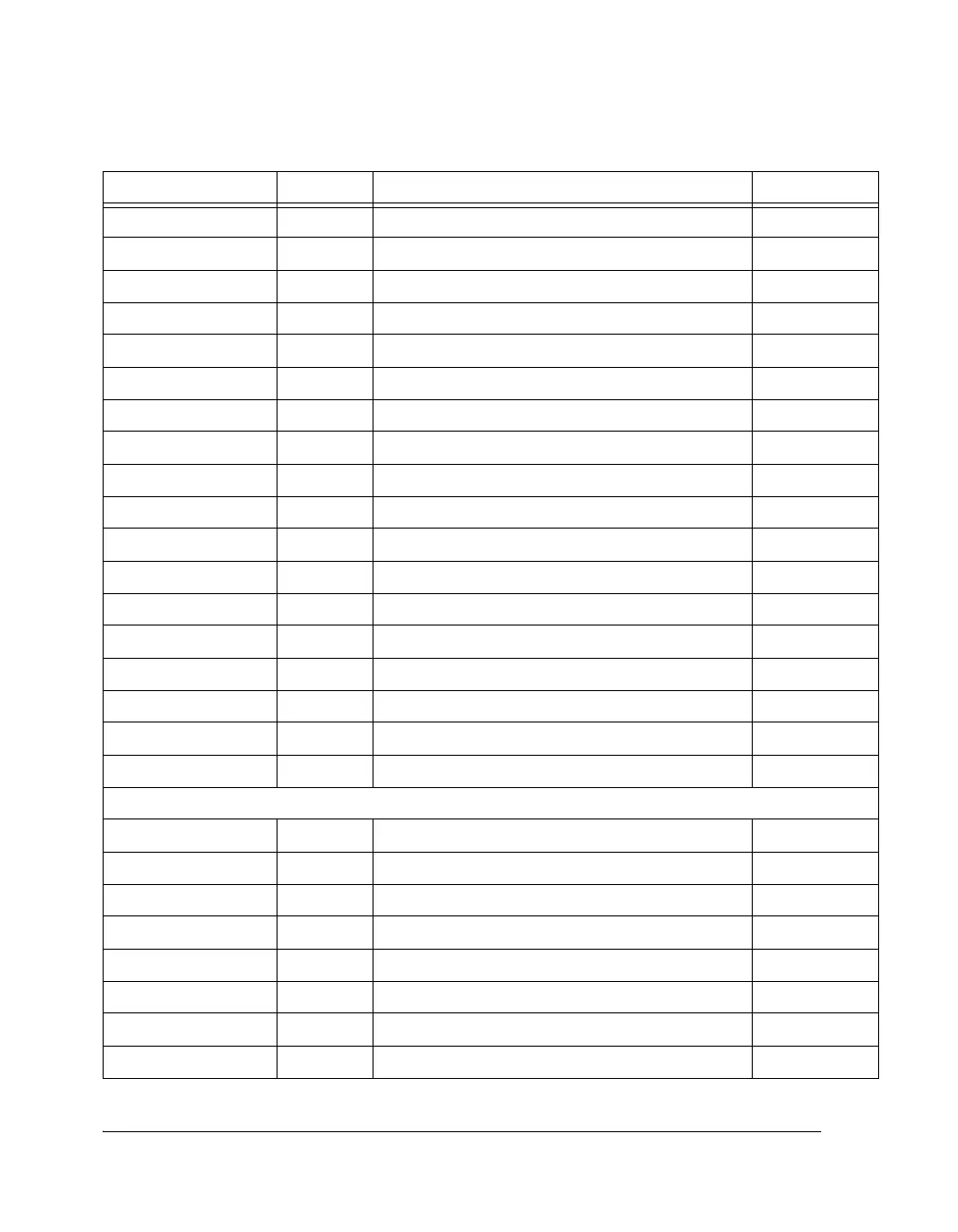

Register Listing

A-274 ADSP-214xx SHARC Processor Hardware Reference

CPEP0 0x1826 External Port CH 0 DMA Chain Pointer 0x0

EBEP0 0x1827 External Port CH 0 DMA External Base Address 0x0

TPEP0 0x1828 External Port CH 0 DMA TAP Pointer 0x0

ELEP0 0x1829 External Port CH 0 DMA External Length 0x0

EPTC0 0x182B External Port CH 0 DMA Delay Line TAP Count 0x0

DFEP0 0x182C External Port CH 0 DMA Data FIFO 0x0

DMAC1 0x180C External Port DMA CH 1 Control 0x0

EIEP1 0x1830 External Port CH 1 DMA External Index Address 0x0

EMEP1 0x1831 External Port CH 1 DMA External Modifier 0x0

ECEP1 0x1832 External Port CH 1 DMA External Count 0x0

IIEP1 0x1833 External Port CH 1 DMA Internal Index Address 0x0

IMEP1 0x1834 External Port CH 1 DMA Internal Modifier 0x0

ICEP1 0x1835 External Port CH 1 DMA Internal Count 0x0

CPEP1 0x1836 External Port CH 1 DMA Chain Pointer 0x0

EBEP1 0x1837 External Port CH 1 DMA External Base Address 0x0

ELEP1 0x1839 External Port CH 1 DMA External Length 0x0

EPTC1 0x183B External Port CH 1 DMA Delay Line TAP Count 0x0

DFEP1 0x183C External Port CH 1 DMA Data FIFO 0x0

DDR2 Controller Registers

DDR2CTL0 0x1812 DDR2 Control 0 0x1800 0018

DDR2CTL1 0x1813 DDR2 Control 1 0x9452 3466

DDR2CTL2 0x1814 DDR2 Control 2 0x422

DDR2CTL3 0x1815 DDR2 Control 3 0x4780

DDR2CTL4 0x1816 DDR2 Control 4 0x8000

DDR2CTL5 0x1817 DDR2 Control 5 0xC000

DDR2RRC 0x181D DDR2 Refresh Rate 0x2800614

DDR2STAT0 0x181E DDR2 Status 0 0x8

Register Mnemonic Address Description Reset

Loading...

Loading...