ADSP-214xx SHARC Processor Hardware Reference A-205

Registers Reference

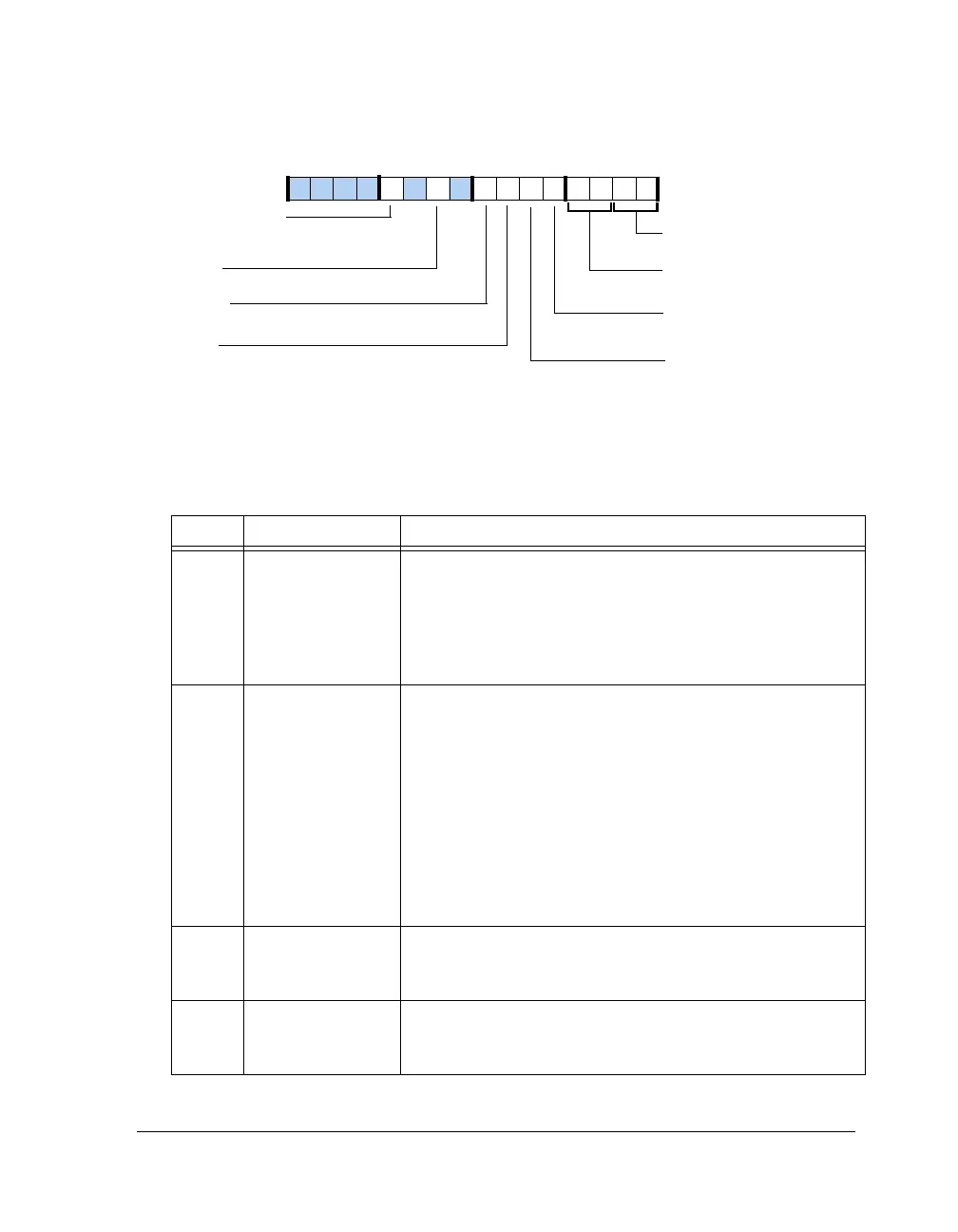

Figure A-108. DIRCTL Register

Table A-109. DIRCTL Register Bit Descriptions (RW)

Bit Name Description

1–0 DIR_BIPHASE Parity Biphase Error Control. When a parity or biphase error

occurs, the audio data will be handled according to these bits.

00 = No action taken

01 = Hold last valid sample

10 = Replace invalid sample with zeros

11 = Reserved

3–2 DIR_LOCK_ERR Lock Error Control. When the DIR_LOCK bit in the DIRSTAT

register is deasserted, it means the PLL has become unlocked and

the audio data is handled according to these bit settings.

00 = No action taken

01 = Hold last valid sample

10 = Send zeros after the last valid sample

11 = Soft mute of the last valid audio is performed (as if NOS-

TREAM is asserted). This is valid only when linear PCM audio

data is in the stream. When non-linear audio data is in the

stream, this mode defaults to the case of

DIR_LOCK_ERR1–0 bits = 10.

4DIR_SCDF_LRSingle-Channel, Double-Frequency Channel Select.

0 = Left channel

1 = Right channel

5DIR_SCDF Single-Channel, Double-Frequency Mode Enable.

0 = 2 channel mode enabled

1 = SCDF mode

DIR_BIPHASE (1–0)

DIR_PLLDIS

Disable PLL

Parity Biphase Error Control

DIR_LOCK_ERR (3–2)

Lock Error Control

DIR_MUTE

Mute

DIR_SCDF

Single-Channel, Double-Fre-

quency Mode Enable

DIR_SCDF_LR

Single Channel Double Fre-

quency Mode Enable

DIR_RESET

Soft Reset

09 837564 2114 12 11 101315

DIR_DTS_CD_4K_EN

DTS_CD 4096 Frames Support

Enable

Loading...

Loading...