Peripherals Routed Through the DPI

A-268 ADSP-214xx SHARC Processor Hardware Reference

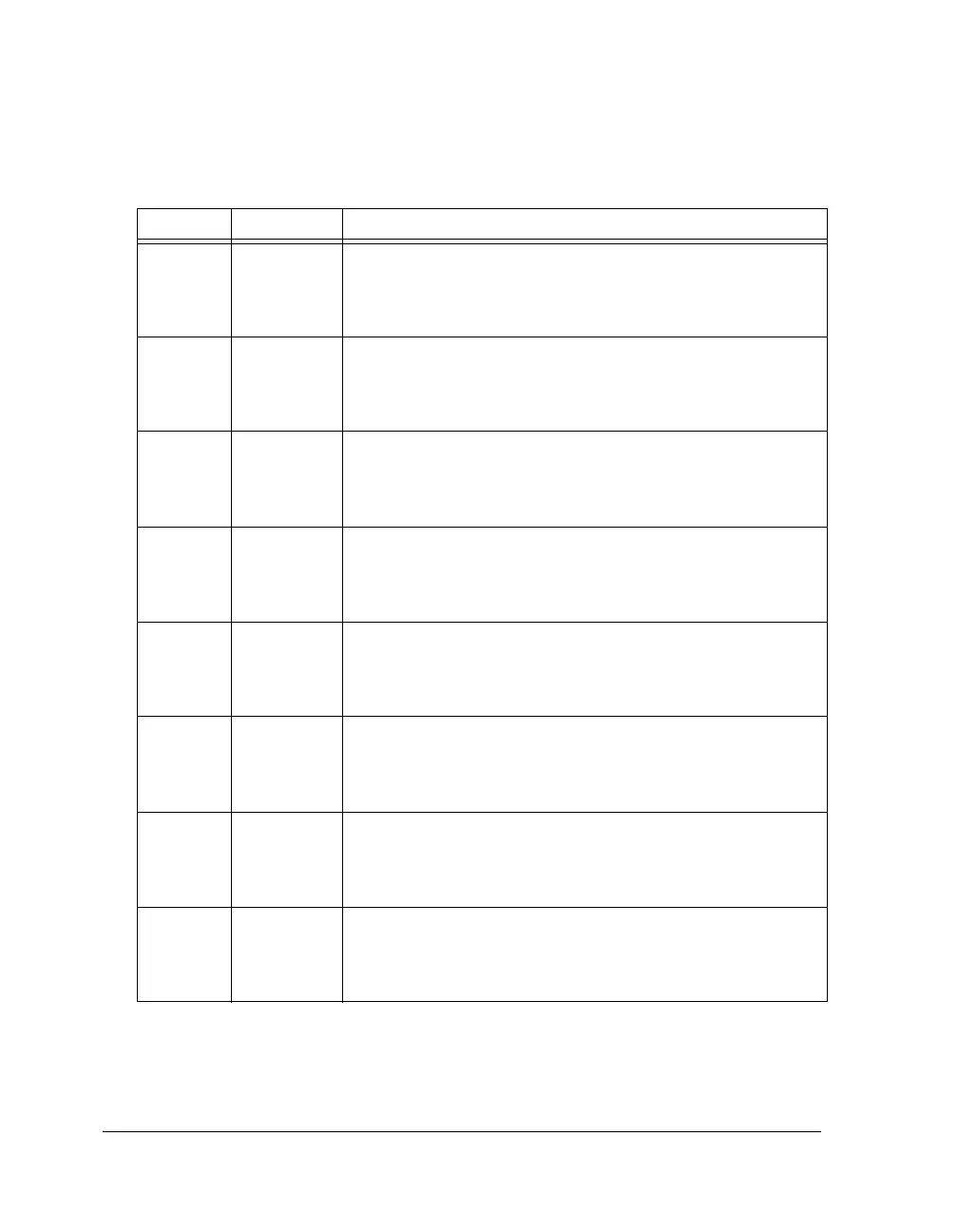

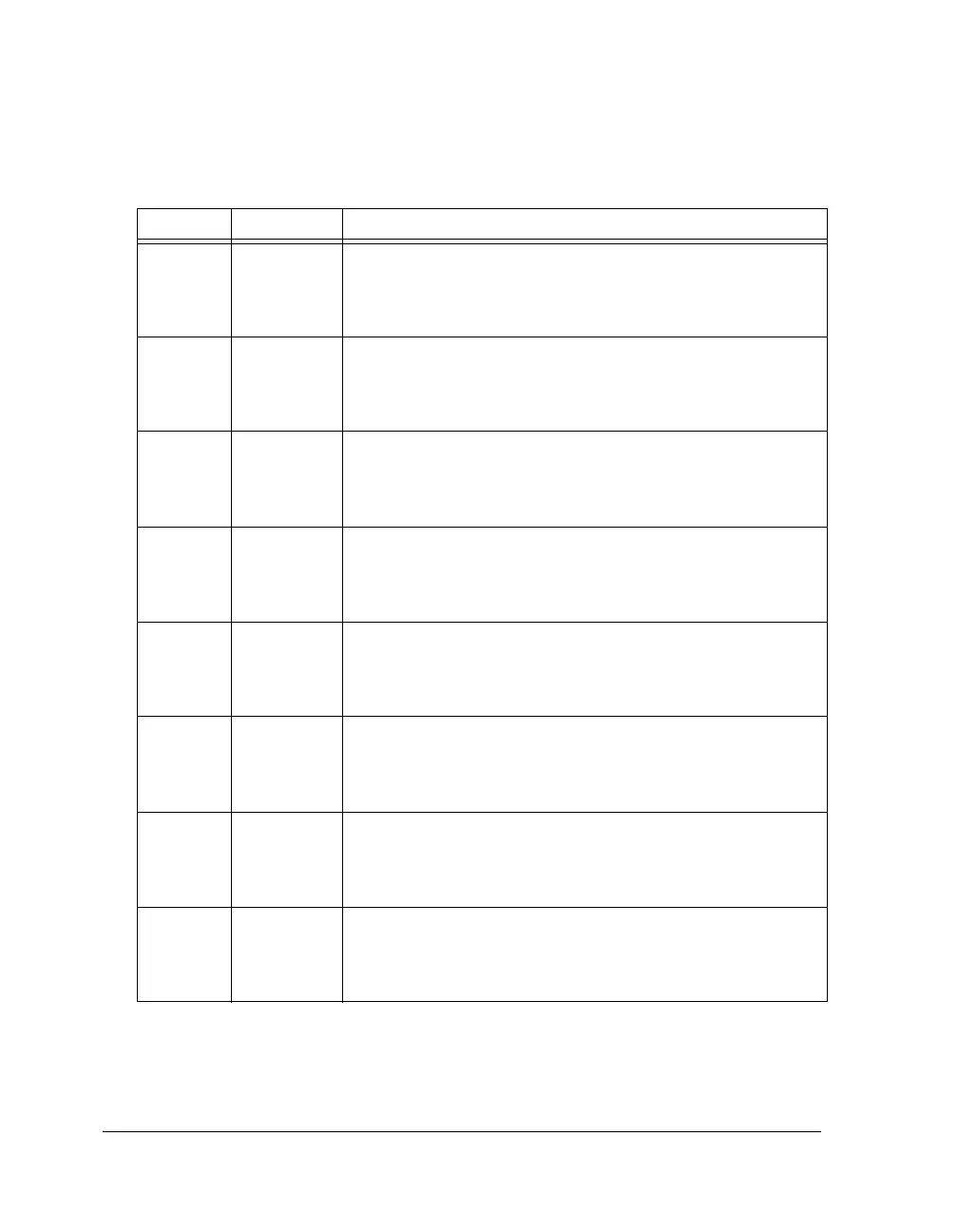

Table A-145. TWIIMASK Register Bit Descriptions (RW)

Bit Name Description

0TWISINITSlave Transfer Initiate Interrupt Enable.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

1TWISCOMPSlave Transfer Complete Interrupt.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

2TWISERRSlave Transfer Error Interrupt.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

3TWISOVF Slave Overflow Interrupt Enable.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

4TWIMCOM Master Transfer Complete Interrupt Enable.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

5TWIMERRMaster Transfer Error Interrupt Enable.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

6TWITXINTTransmit FIFO Service Interrupt Enable.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

7TWIRXINTReceive FIFO Service Interrupt Enable.

0 = The corresponding interrupt source is prevented from asserting

the interrupt output.

1 = The corresponding interrupt source asserts the interrupt output.

Loading...

Loading...