ADSP-214xx SHARC Processor Hardware Reference A-279

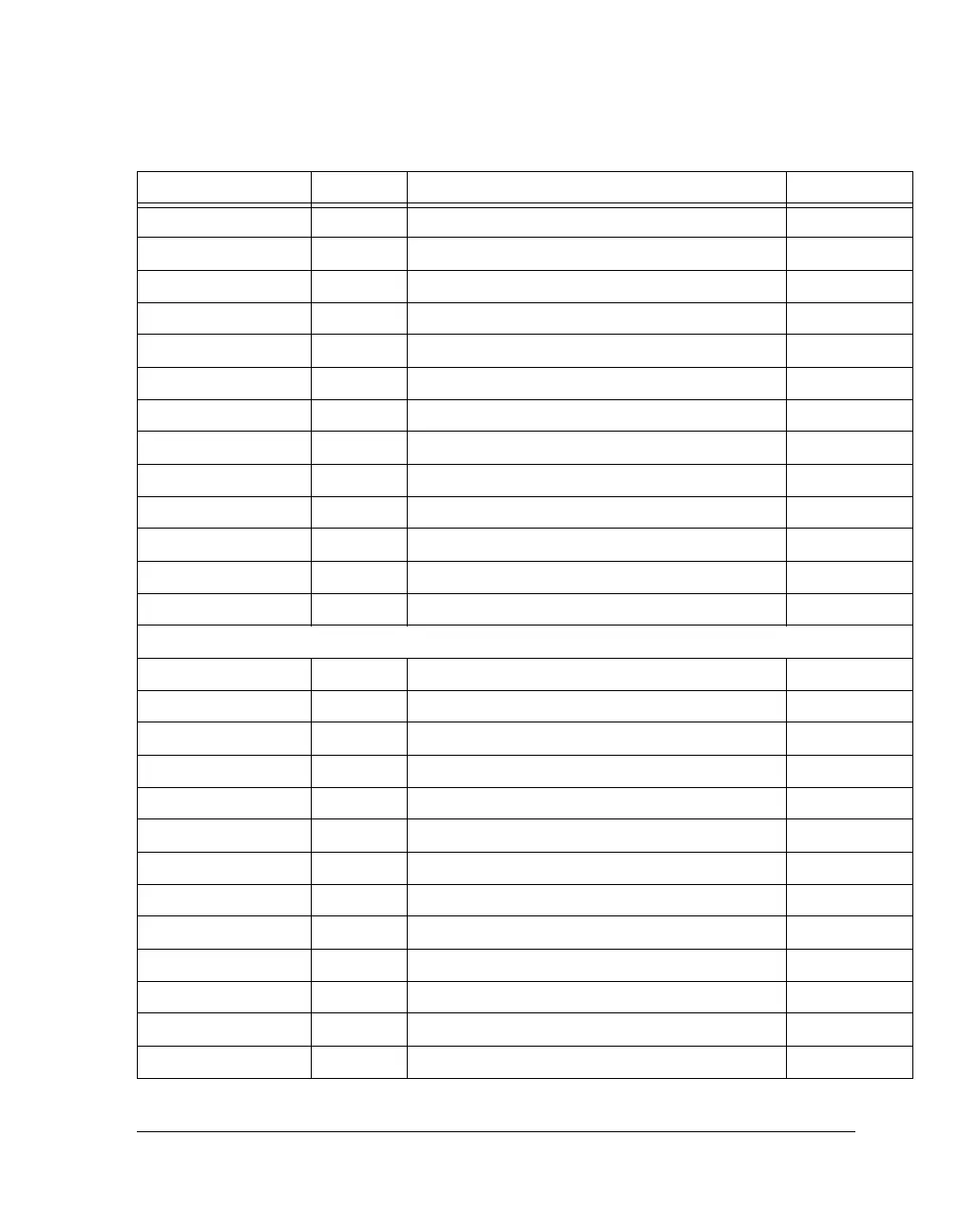

Registers Reference

CPSP3A 0x44B Points to Next DMA Parameters 0x0

IISP3B 0x44C Internal Memory DMA Address 0x0

IMSP3B 0x44D Internal Memory DMA Access Modifier 0x0

CSP3B 0x44E Contains Number of DMA Transfers Remaining 0x0

CPSP3B 0x44F Points to Next DMA Parameters 0x0

TXSP2A 0x460 SPORT 2A Transmit Data 0x0

RXSP2A 0x461 SPORT 2A Receive Data 0x0

TXSP2B 0x462 SPORT 2B Transmit Data 0x0

RXSP2B 0x463 SPORT 2B Receive Data 0x0

TXSP3A 0x464 SPORT 3A Transmit Data 0x0

RXSP3A 0x465 SPORT 3A Receive Data 0x0

TXSP3B 0x466 SPORT 3B Transmit Data 0x0

RXSP3B 0x467 SPORT 3B Receive Data 0x0

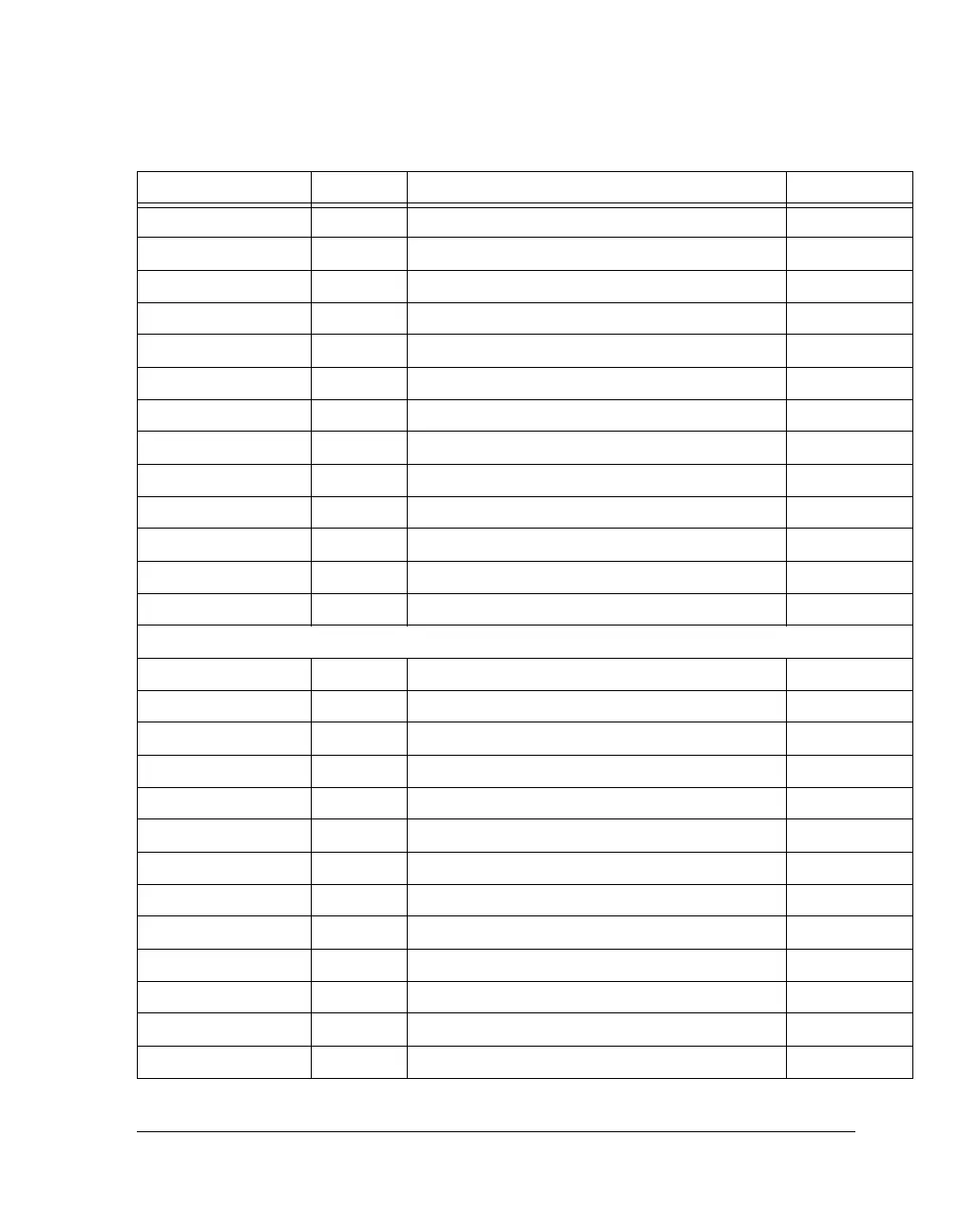

Serial Port 4 and 5 Registers

SPCTL4 0x800 SPORT 4 Control 0x0000 0000

SPCTL5 0x801 SPORT 5 Control 0x0000 0000

SPCTLN4 0x81A SPORT 4 Control Register 2 0x0000 0000

SPCTLN5 0x819 SPORT 5 Control Register 2 0x0000 0000

DIV4 0x802 SPORT 4 Divisor for TX/RX SCLK4 and FS4 0x0

DIV5 0x803 SPORT 5 Divisor for TX/RX SCLK5 and FS5 0x0

SPMCTL4 0x804 SPORT 4 TDM Control 0x0

MT4CS0 0x805 SPORT 4 TDM TX Select, CH31–0 0x0

MT4CS1 0x806 SPORT 4 TDM TX Select, CH63–32 0x0

MT4CS2 0x807 SPORT 4 TDM TX Select, CH95–64 0x0

MT4CS3 0x808 SPORT 4 TDM TX Select, CH127–96 0x0

MR5CS0 0x809 SPORT 5 TDM RX Select, CH31–0 0x0

MR5CS1 0x80A SPORT 5 TDM RX Select, CH63–32 0x0

Register Mnemonic Address Description Reset

Loading...

Loading...