ADSP-214xx SHARC Processor Hardware Reference 9-15

Digital Application/Digital Peripheral Interfaces

For each bidirectional line, the SPORT provides three separate signals.

For example, a SPORT clock has three separate SRU connections (instead

of one physical pin):

• input clock to the SPORT (

SPORTx_CLK_I)

• output clock of the SPORT (SPORTx_CLK_O)

• output enable clock of the SPORT (

SPORTx_CLK_PBEN_O)

If the SPORT operates in master mode, the

SPORTx_CLK_O and

SPORTx_CLK_PBEN signals are automatically driven. If operating in slave

mode, the SPORTx_CLK_O and SPORTx_CLK_PBEN signals are automatically

disabled and the

SPORTx_CLK_I signal expects an external clock.

The input and output signal pair is never used simultaneously. The

pin enable signal dictates which of the two SPORT lines appear at

the DAI pin at any given time. By connecting all three signals

through the SRU, the standard SPORT configuration registers

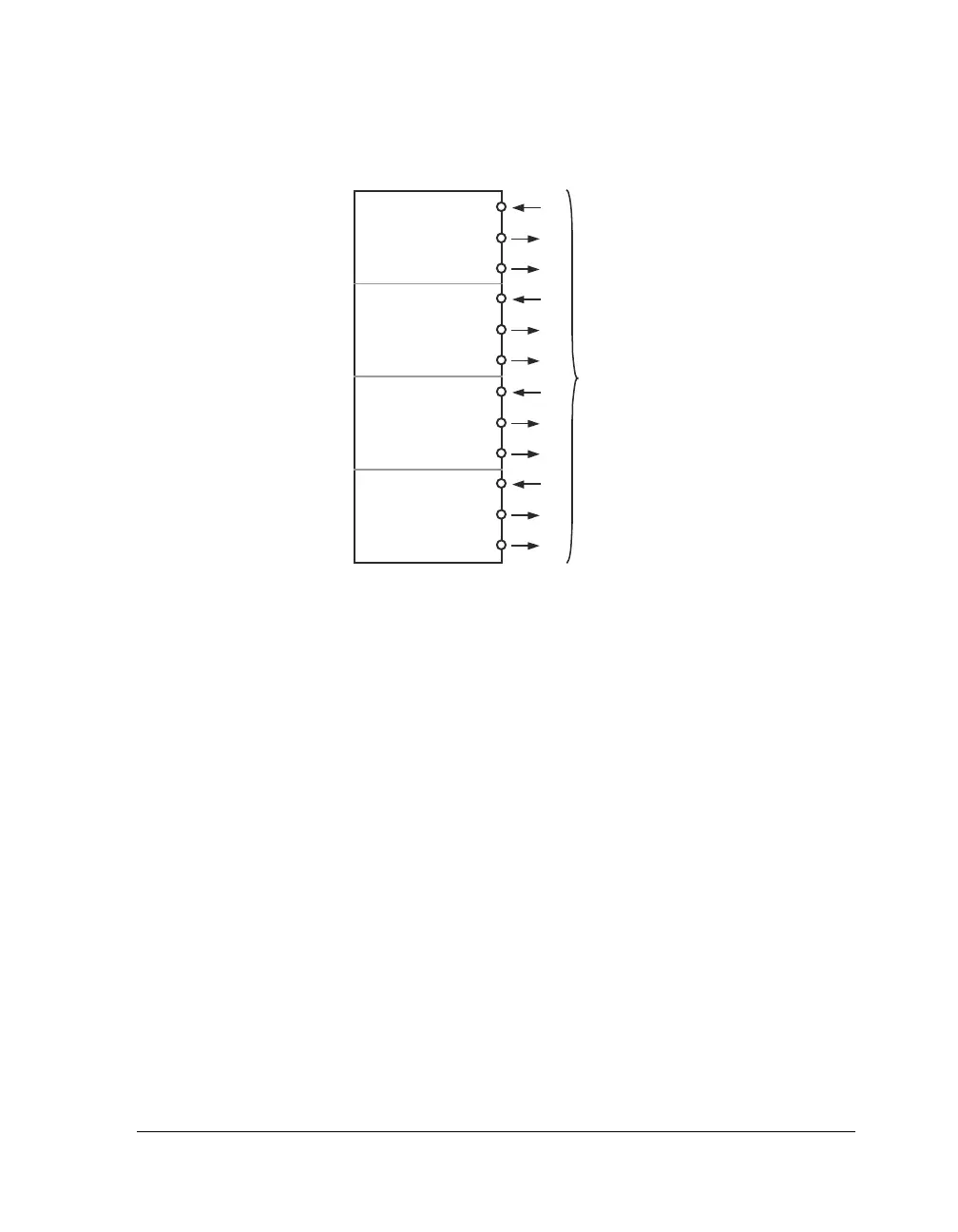

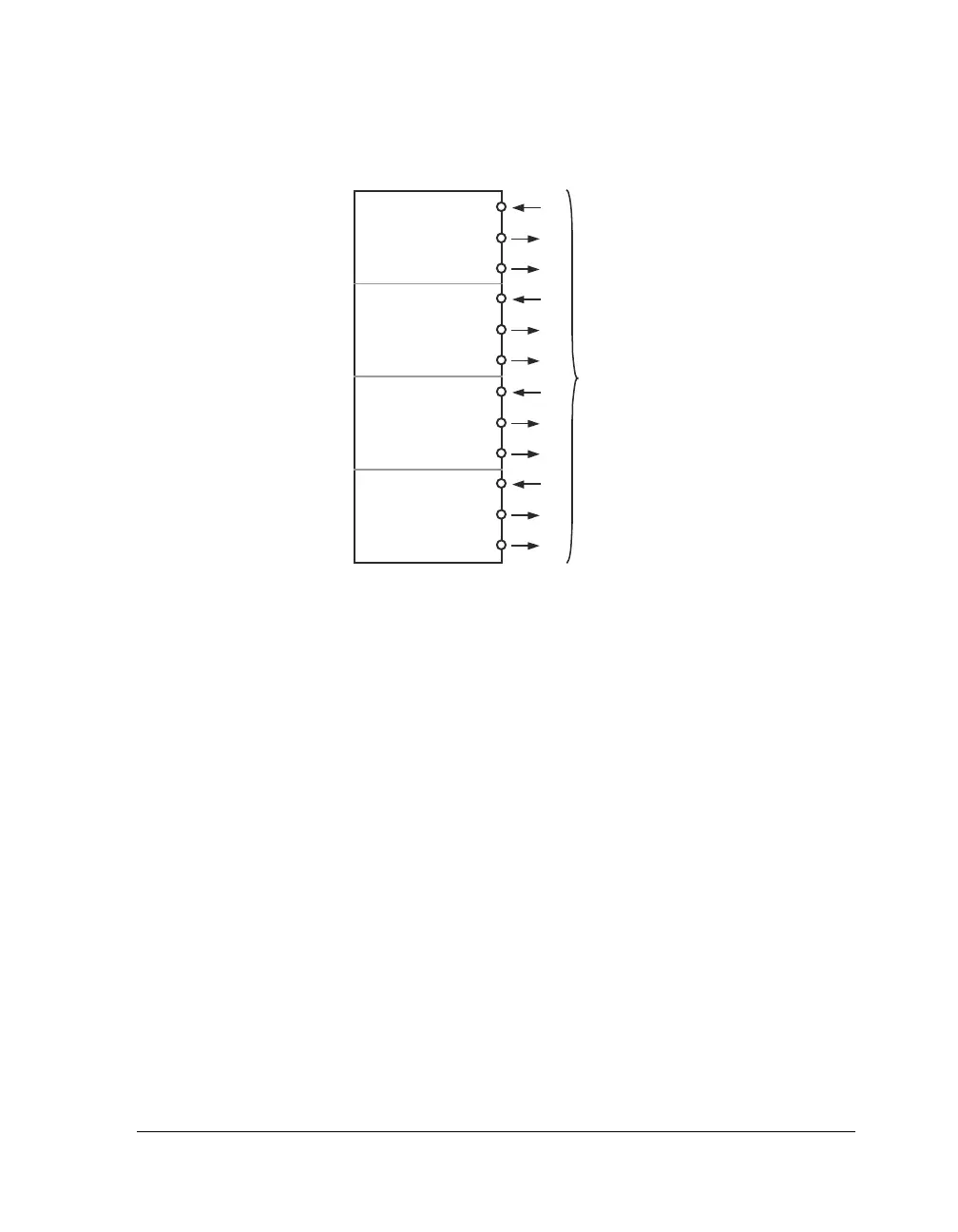

Figure 9-8. SRU Connections for SPORT0

Interface

to SRU

SPORT0_DA_O

SPORT0_DA_I

SPORT0_DA_PBEN_O

SPORT0_FS_O

SPORT0_FS_I

SPORT0_FS_PBEN_O

SPORT0_CLK_O

SPORT0_CLK_I

SPORT0_CLK_PBEN_O

SPORT0_DB_O

SPORT0_DB_I

SPORT0_DB_PBEN_O

Loading...

Loading...