S/PDIF Receiver

13-14 ADSP-214xx SHARC Processor Hardware Reference

The input to the receiver (

DIR_I) is a biphase encoded signal that may

contain two audio channels (compressed or linear PCM) or non-audio

data. The receiver decodes the single biphase encoded stream, producing

an I

2

S compatible serial data output that consists of a serial clock, a

left-right frame sync, and data (channel A/B). It provides the programmer

with several methods of managing the incoming status bit information.

The S/PDIF receiver receives any S/PDIF stream with a sampling fre-

quency range of 32 kHz – 15% to 192 kHz + 15% range.

The channel status bits are collected into memory-mapped registers, while

other channel status and user bytes must be handled manually. The block

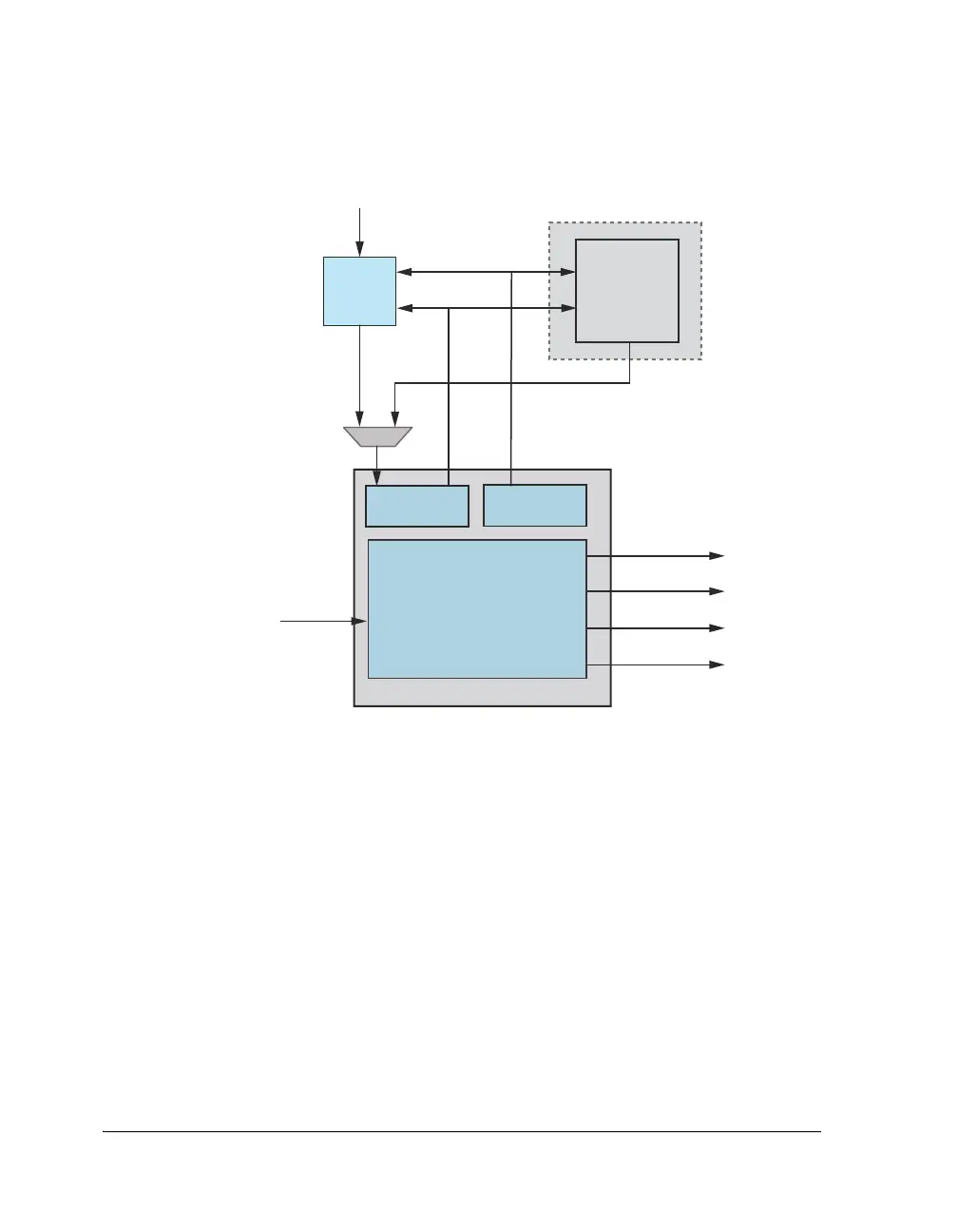

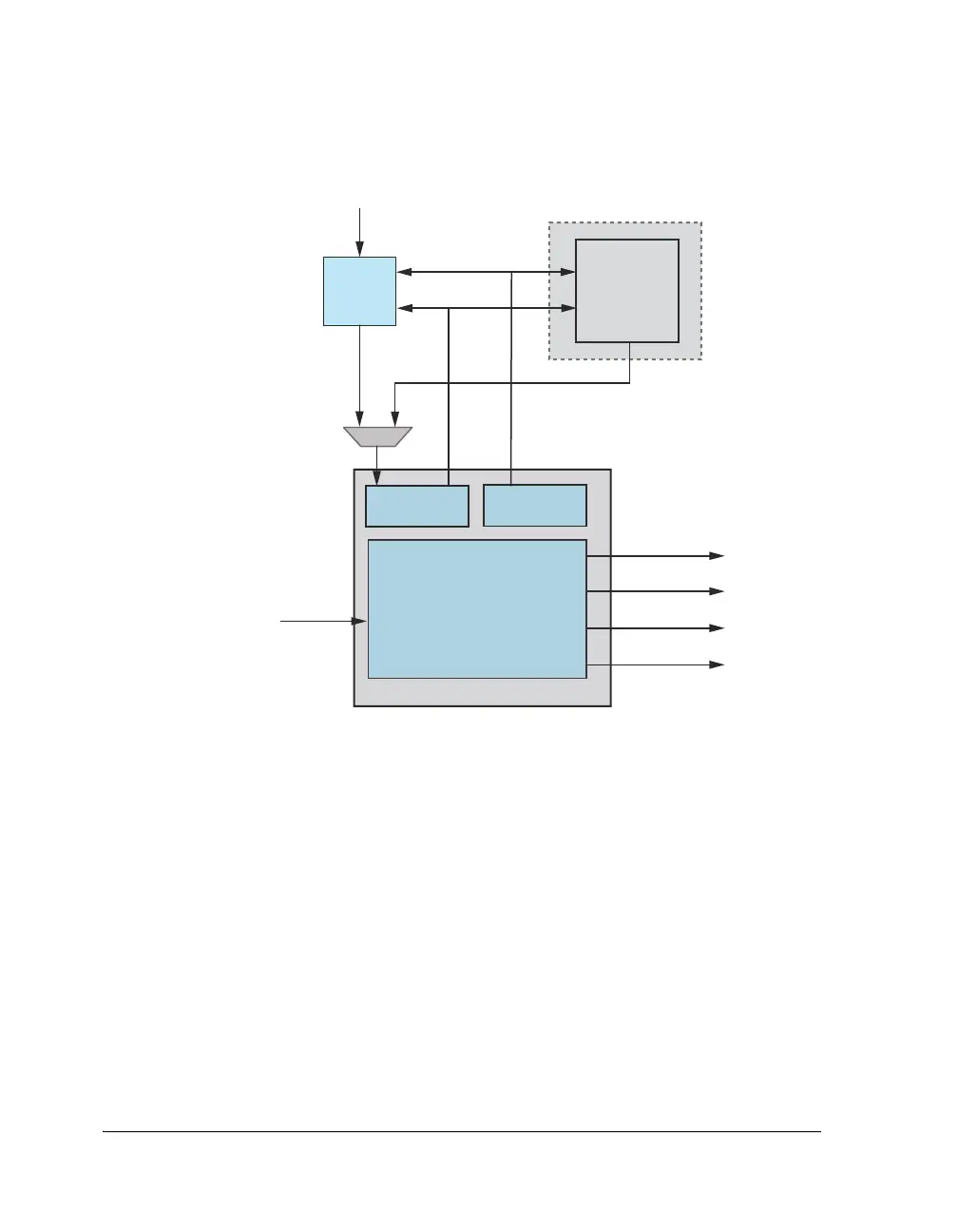

Figure 13-8. S/PDIF Receiver Block Diagram

DIR_CLK_O

DIR_FS_O

LRCLK_REF_O

DIR_DAT_O

PROCESSOR

PLL

LRCLK_FB_O

BIPAHSE

DECODING

REFRAMING

LOGIC

DIR_I

(BIPHASE STREAM)

S/PDIF RECEIVER

CLK

DIGITAL

PLL

DIR_TDMCLK_O

ANALOG

PLL

OFF-CHIP

REFIN

FBIN

FEEDBACK

DIVIDER = 512

STREAM

PREAMBLE

SPDIF_EXTPLLCLK_I

512 x FS

INT

PLLCLK

Loading...

Loading...