ADSP-214xx SHARC Processor Hardware Reference 23-9

System Design

The ACK pin is disabled during external port booting.

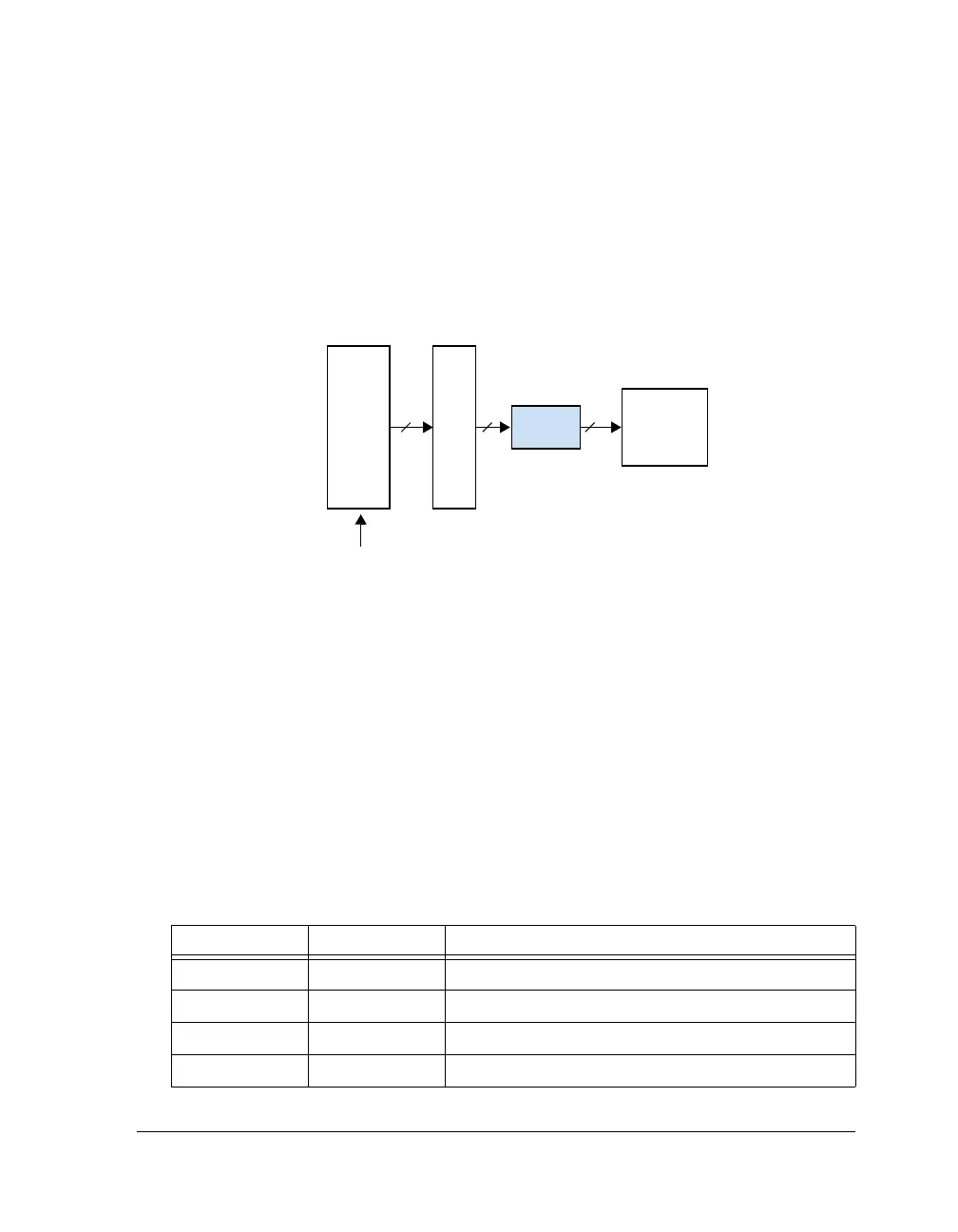

The received data streams of 4x8-bit data words are packed by the AMIRX

buffer into 32-bit words least significant bit (LSB) first, and passed

through the DMA’s 6 deep external port buffer DFEP0 into the internal

memory (Figure 23-3).

The external port DMA channel 0 (DMAC0) is used when downloading the

boot kernel information to the processor. At reset, the DMA parameter

registers are initialized to the values listed in Table 23-4.

In this configuration, the loader kernel is read via DMA from the FLASH.

If the application needs to speed-up read accesses, programs should

change the wait states (WS bits, see Table 23-2) in the kernel file. After the

kernel is executed, the new wait state settings are applied and processor

booting continues.

Figure 23-3. External Port Data Packing

Table 23-2. AMICTL1 Boot Settings (0x5C1)

Bit Name Setting

0 AMIEN AMI enable (set = 1)

2–1 BW Bus width = 8-bit (00)

3 PKDIS Packing, 8-bit to 32-bit (cleared = 0)

4 MSWF Most significant word first (cleared = 0)

AMIRX

DFEP0

Internal

Memory

32 32

32

DMA

8-bit to 32-bit packing

DATA[7:0]

Loading...

Loading...