Processor Booting

23-10 ADSP-214xx SHARC Processor Hardware Reference

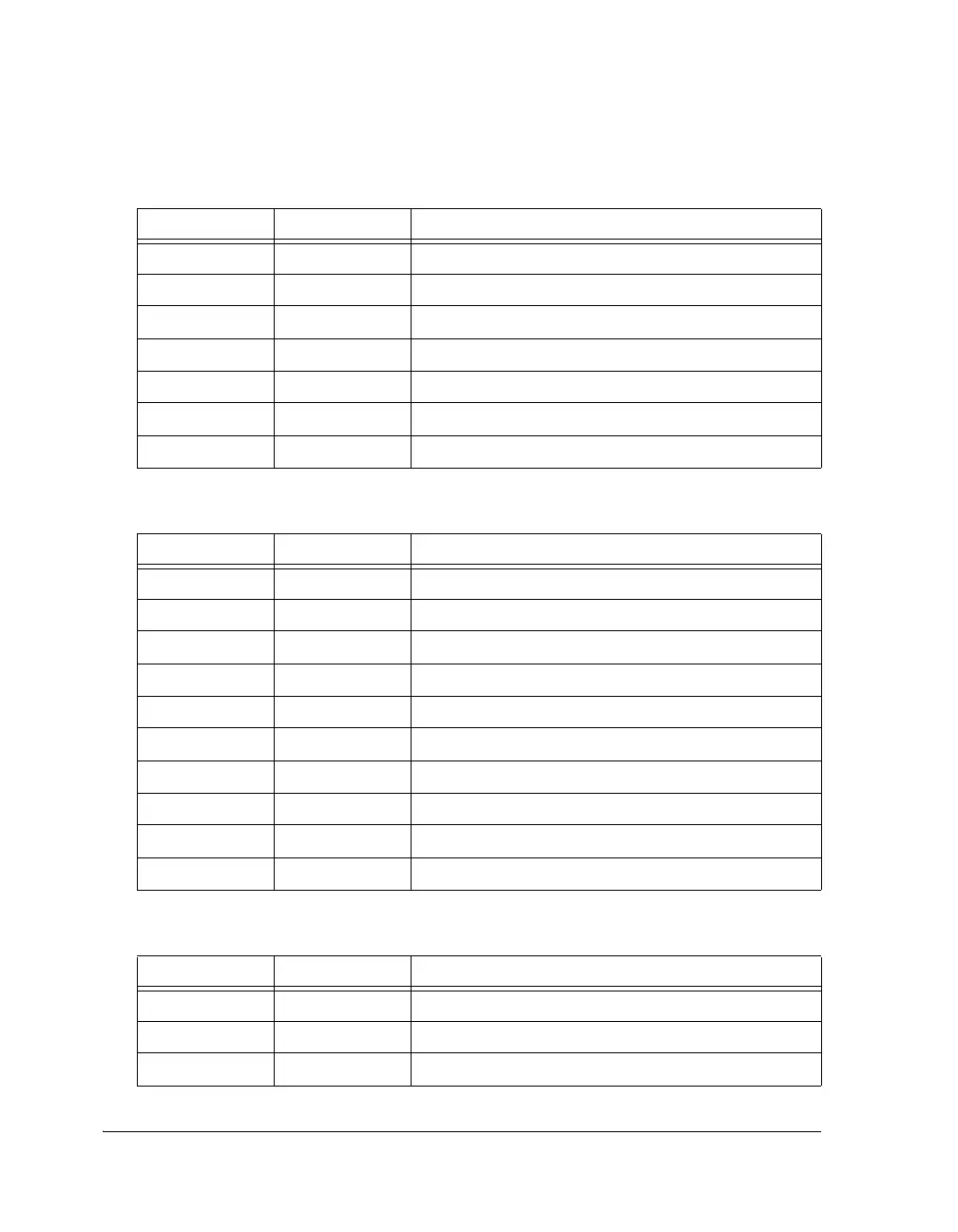

5 ACKEN ACK pin disabled (cleared = 0)

10–6 WS 23 wait state cycles = 10111

13–11 HC Bus hold cycle at the end of write access = 000

16–14 IC No bus idle cycle = 000

17 FLSH Buffer holds data (cleared = 0)

20–18 RHC Read hold cycle at the end of read access = 000

21 PREDIS Disable Predictive Reads (cleared = 0)

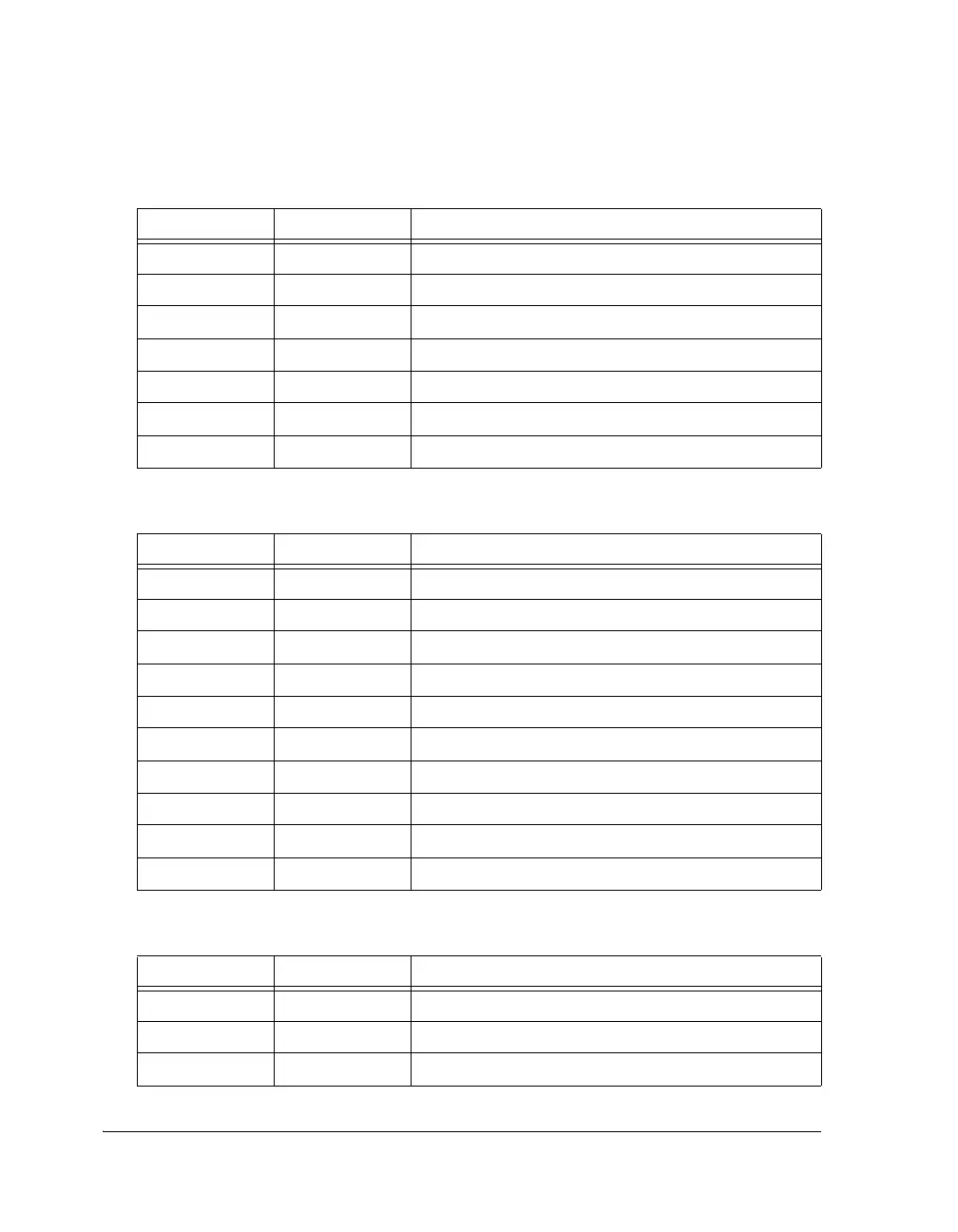

Table 23-3. EPCTL Boot Settings (0xF0)

Bit Name Setting

0 B0SD No SDRAM bank 0 (cleared = 0)

1 B1SD No SDRAM bank 1 (cleared = 0)

2 B2SD No SDRAM bank 2 (cleared = 0)

3 B3SD No SDRAM bank 3 (cleared = 0)

5–4 EPBR Rotating priority core vs. DMA (11)

7–6 DMAPR Rotating priority EPDMA ch0 vs. EPDMA ch1 (11)

10–8 FRZDMA No DMA freezing (00)

14–12 FRZCR No core freezing (00)

18–15 DATE No pack mode (0000) (ADSP-2147x/2148x only)

21–19 FRZSP No SPORT DMA freezing (000)

Table 23-4. DMAC0 Boot Settings (0x1000001)

Bit Name Setting

0 DMAEN DMA enabled (set = 1)

1 TRAN Write to internal memory (cleared = 0)

2 CHEN No DMA chaining (cleared = 0)

Table 23-2. AMICTL1 Boot Settings (0x5C1) (Cont’d)

Bit Name Setting

Loading...

Loading...