ADSP-214xx SHARC Processor Hardware Reference A-27

Registers Reference

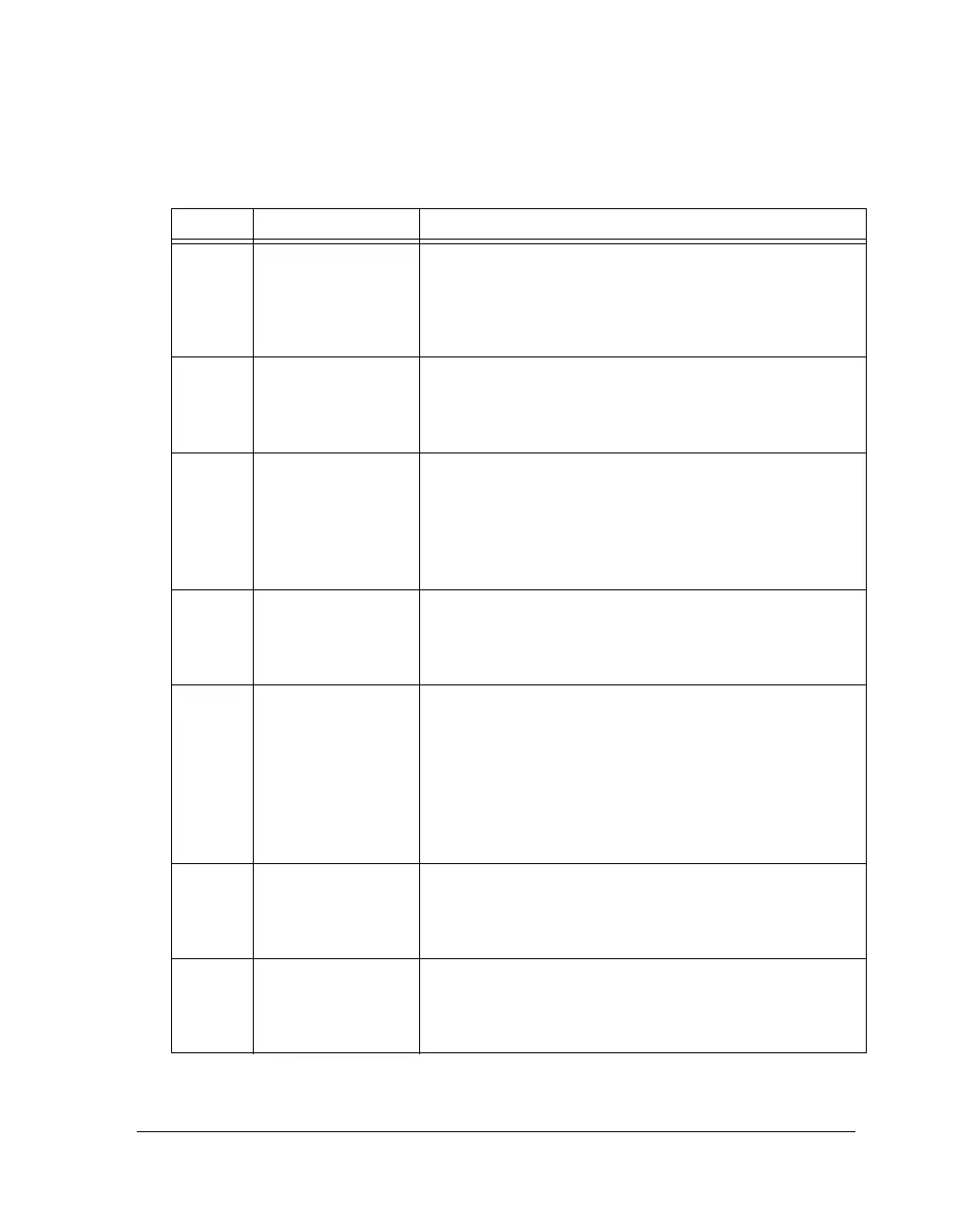

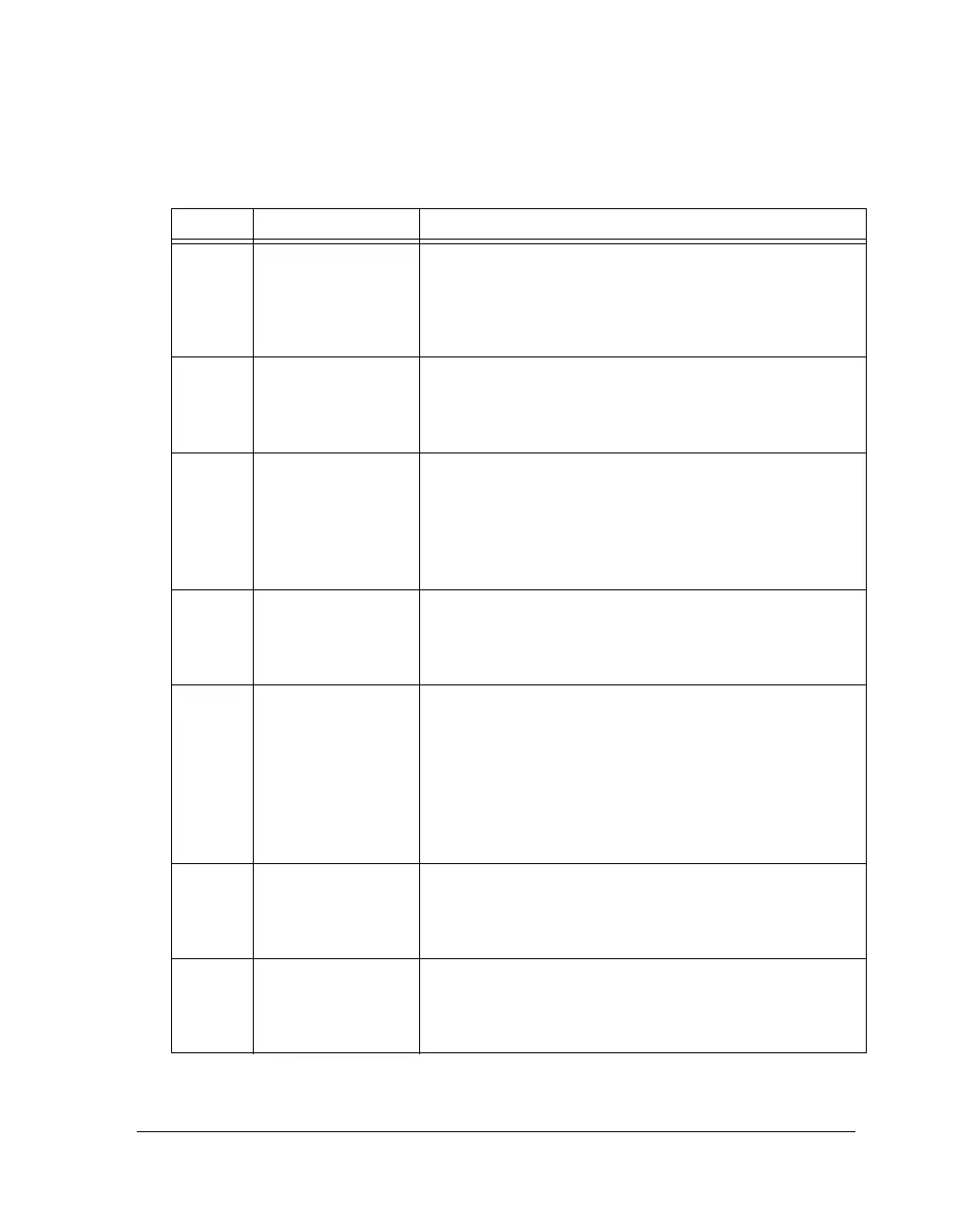

11–9 DDR2RAW Row Address Width.

000 = 8 bits

001 = 9 bits

...

111 = 15 bits

12 (WO) FEMR2 Force EMR2 Register Write. Forces EMR2 only if the banks

are all precharged.

0 = No effect

1 = Force EMR2 register write to DDR2

13 (WO) FDLLCAL Force DLL External Bank Calibration. Triggers a DLL calibra-

tion sequence to all of the external banks assigned to DDR2

controller in the EPCTL register (BxSD bits). Note for each

bank the calibration takes 300 DDR2 cycles.

0 = No effect

1 = Trigger DLL for external bank calibration

14 DDR2ADDRMODE Select the Address Mapping. This bit selects how the data are

stored in the DDR2 memory.

0 = Page interleaving map (consecutive pages/different banks)

1 = Bank interleaving map (consecutive banks)

15 (WO) DDR2PSS Power-Up Sequence Start. The power-up sequence is started

by setting this bit. Note that the entire power-up sequence

takes many cycles to complete. The more external banks

assigned, the longer the power-up time.

0 = No effect

1 = Trigger power-up sequence

Note that the power-up sequence does NOT require a user

access to be executed.

16 DDR2WDTHx16 External Data Path Width. Programs should always set (=1)

this bit.

0 = Reserved

1 = 16-bit

17 (WO) FEMR3 Force EMR3 Register Write. Forces EMR3 only if the banks

are all precharged.

0 = No effect

1 = Force EMR3 register write to DDR2

Table A-11. DDR2CTL0 Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...