ADSP-2146x External Port Registers

A-30 ADSP-214xx SHARC Processor Hardware Reference

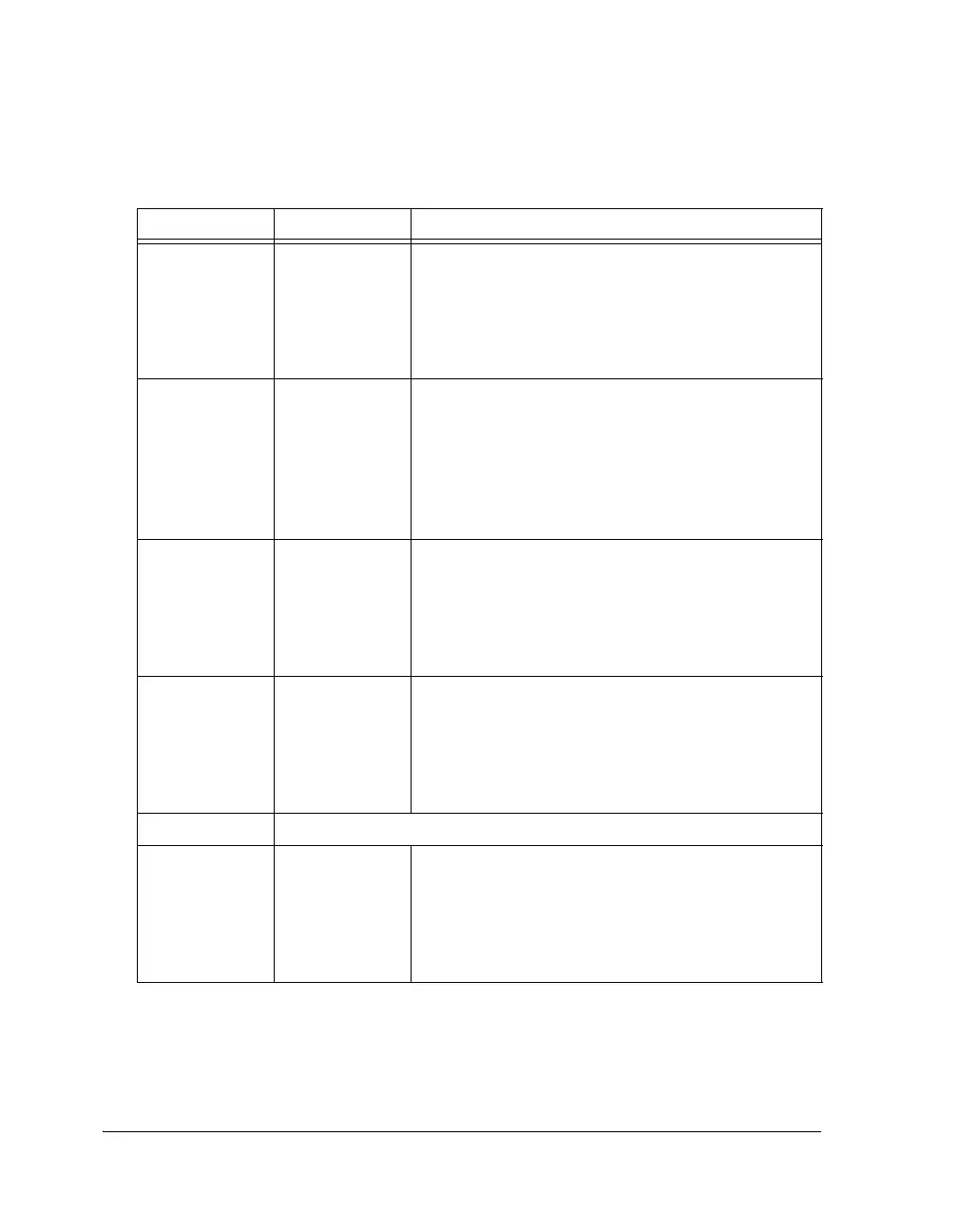

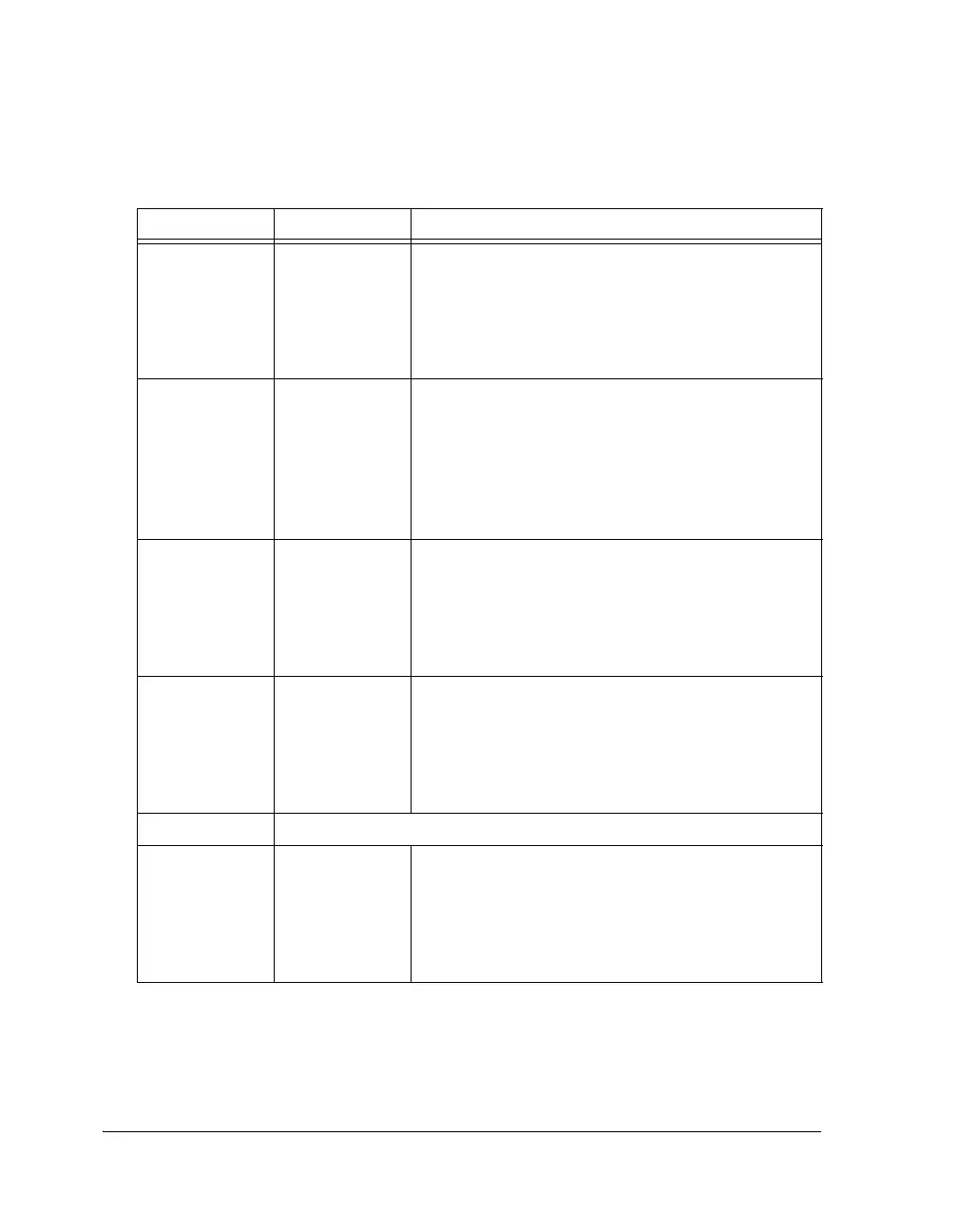

Table A-12. DDR2CTL1 Register Bit Descriptions (RW)

Bit Name Description

4–0 DDR2TRAS Row Active Time.

00000 = Reserved

00001 = 1 clock cycle

00010 = 2 clock cycles

…

11111 = 31 clock cycles

8–5 DDR2TRP Row Precharge Time. Note that for 8 banked devices the

timing spec becomes t

RP

+ 1t

CK

.

0000 = Reserved

0001 = 1 clock cycle

0010 = 2 clock cycles

…

1111 = 15 clock cycles

11–9 DDR2TWTR Write t o Read Delay.

000 = Reserved

001 = 1 clock cycle

010 = 2 clock cycles

…

111 = 7 clock cycles

15–12 DDR2TRCD RAS to CAS Delay.

000 = Reserved

001 = 1 clock cycle

010 = 2 clock cycles

…

111 = 7 clock cycles

18–16 Reserved

21–19 DDR2TRTP Read to Precharge Delay.

000 = Reserved

001 = 1 clock cycle

010 = 2 clock cycles

…

111 = 7 clock cycles

Loading...

Loading...