ADSP-2146x External Port Registers

A-32 ADSP-214xx SHARC Processor Hardware Reference

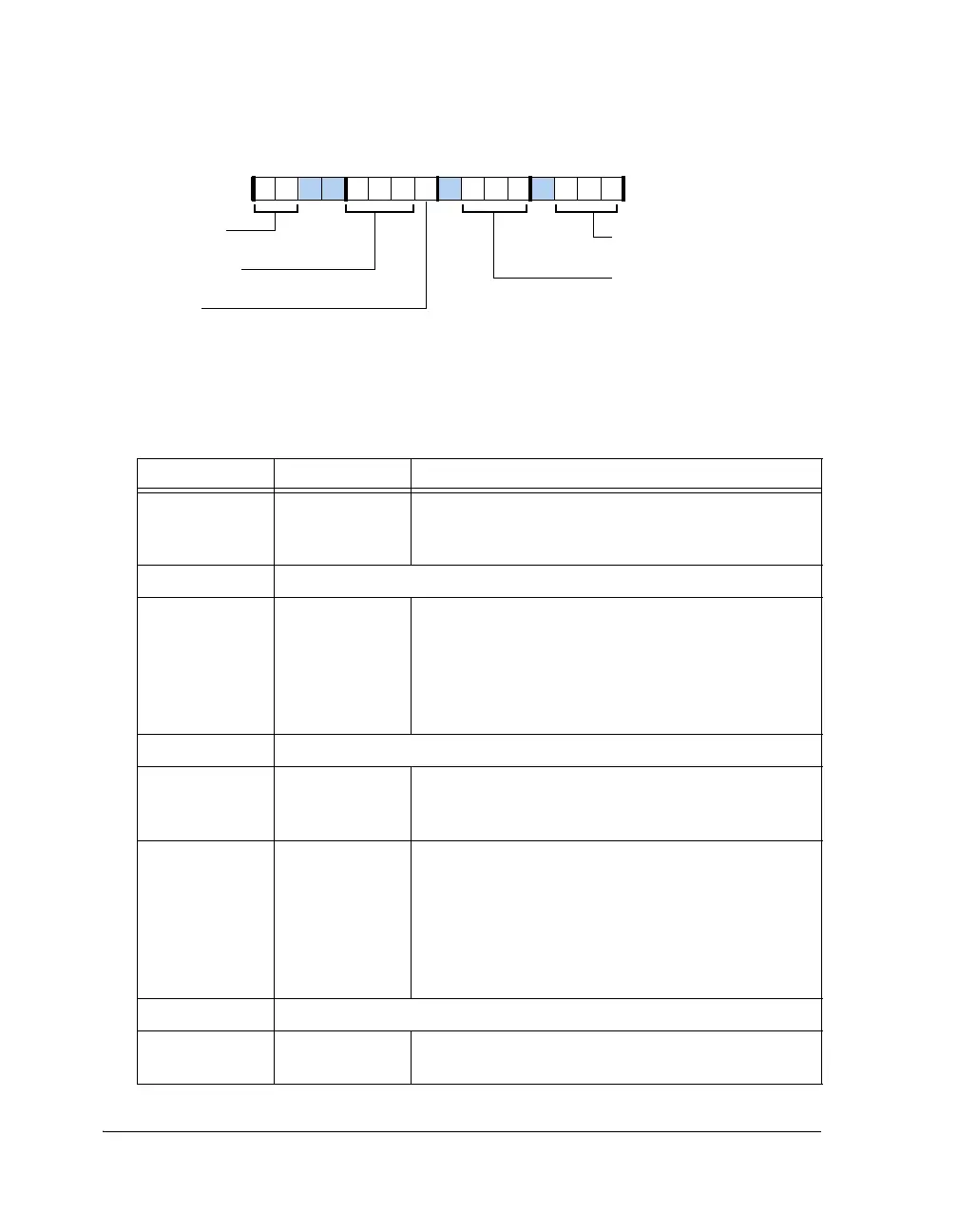

Figure A-11. DDR2CTL2 Register

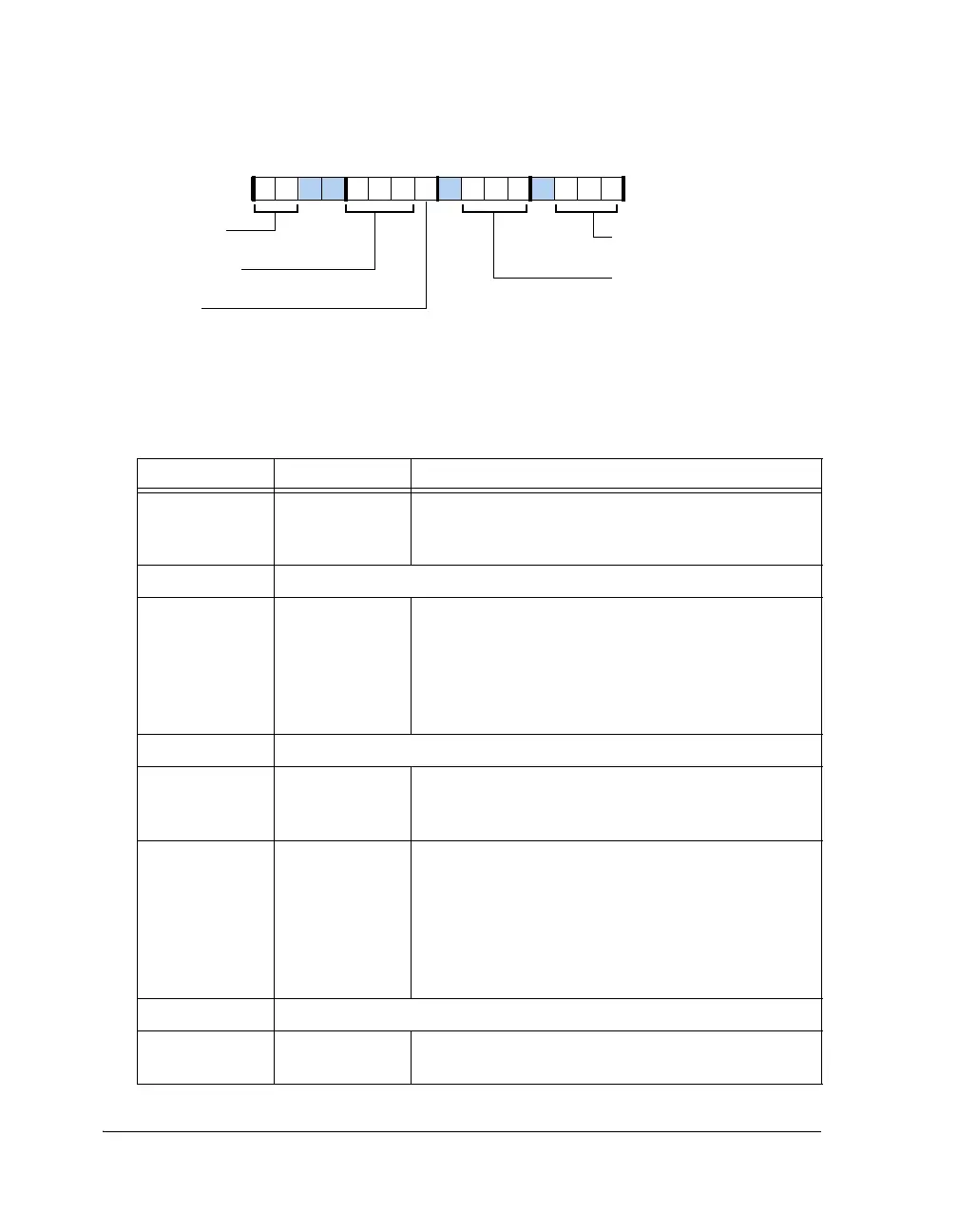

Table A-13. DDR2CTL2 Register Bit Descriptions (RW)

Bit Name Description

2–0 DDR2BL Burst Length.

010 = BL = 4

All other settings reserved.

3 Reserved

6–4 DDR2CAS CAS Latency.

000 = Reserved

001 Reserved

010 2 clock cycles

…

111 7 clock cycles

7 Reserved

8 DDR2DLLRST DLL Reset.

0 = Normal

1 = Reset

11–9 DDR2TWR Write Recover y Time.

000 = Reserved

001 = 2 clock cycle

010 = 3 clock cycles

...

110 = 7 clock cycles

111 = Reserved

12–13 Reserved

15–14 DDR2MR Mode Register.

Must be set to 00.

DDR2BL (2–0)

Burst Length

DDR2DLLRST

DLL Reset

DDR2CAS (6–4)

CAS Latency

DDR2DTWR (11–9)

Write Recovery Time

DDR2MR (15–14)

Mode Register

09 837564 2114 12 11 101315

Loading...

Loading...