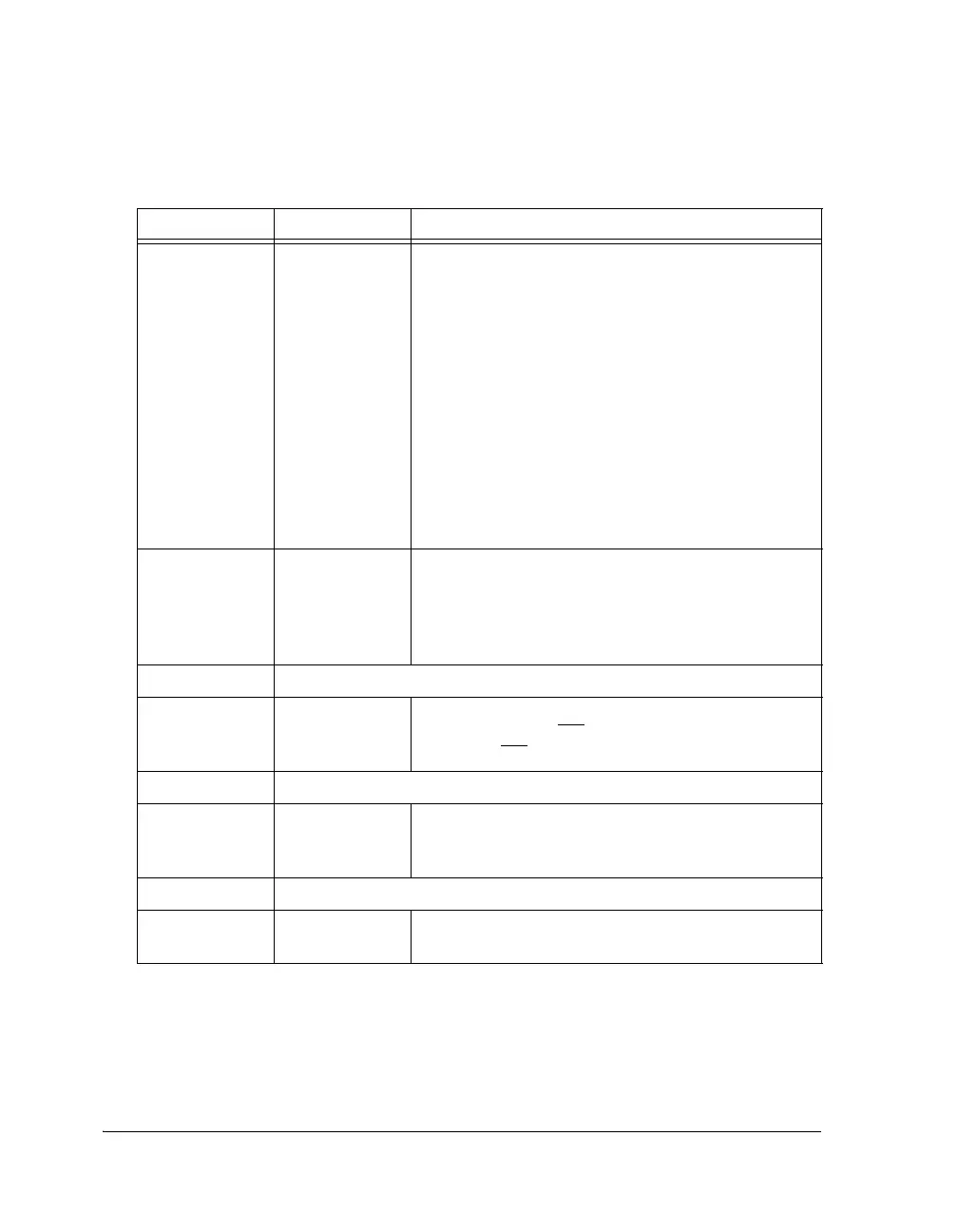

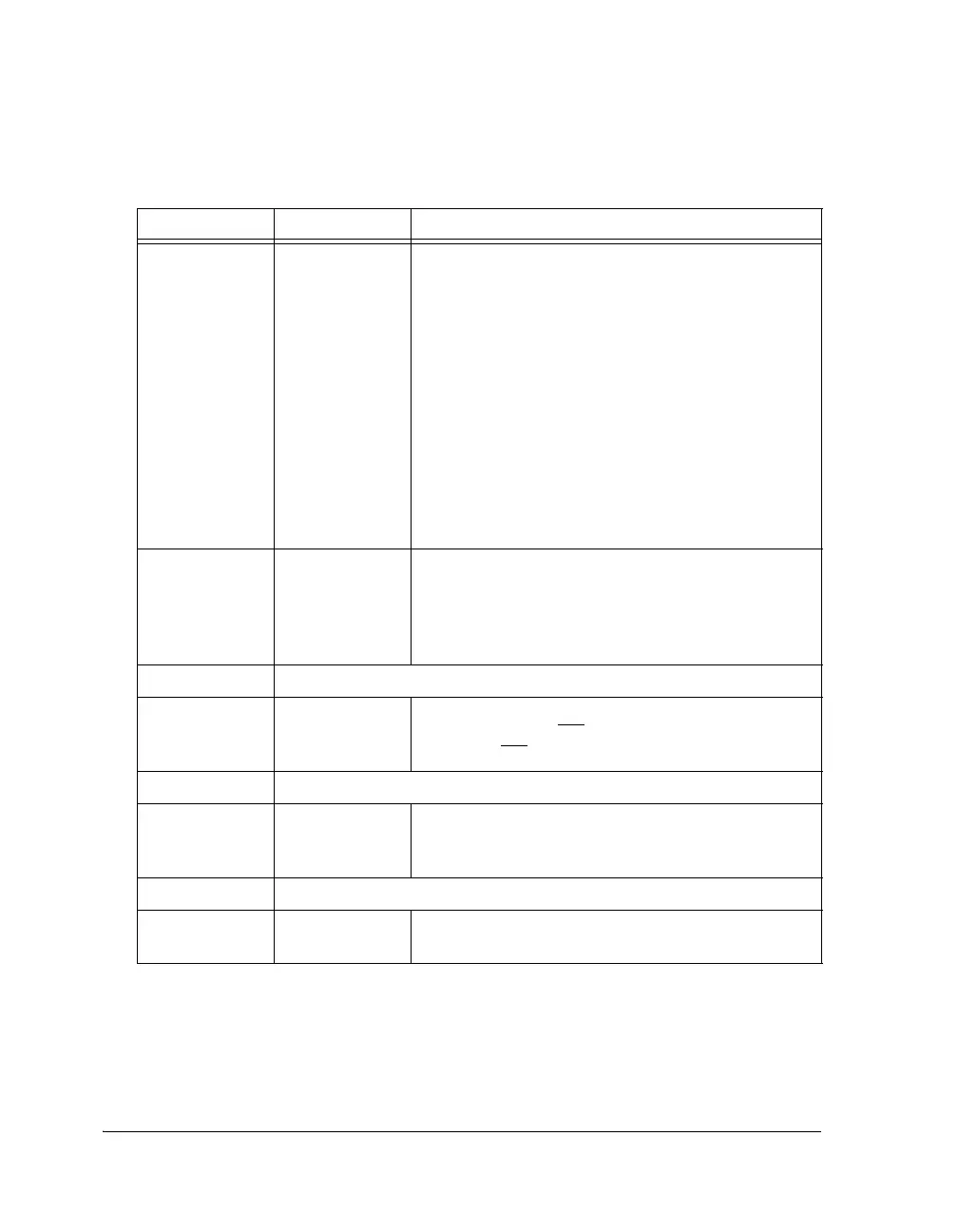

ADSP-2146x External Port Registers

A-34 ADSP-214xx SHARC Processor Hardware Reference

5–3 DDR2AL Additive Latency. Additive latency reduces command bus

conflicts to enable commands to be issued more effi-

ciently. Note thate the DDR2 controller performance is

primary regardless of the AL settings.

000 = 0 clock cycles.

001 = 1 clock cycles.

…

101 = 5 clock cycles.

110, 111 = Reserved.

The basic rule for additive latency is defined as:

AL <= t

RCDmin–1

. Example: t

RCD

is 4 cycles then

AL = 3–0.

If AL = 4, tRCD is increased by 1 cycle, increasing overall

latency.

6, 2 DDR2ODT On Die Termination Value.

00 = ODT disabled

01 = 75 ohm

10 = 150 ohm

11 = 50 ohm

9–7 Reserved

10 DDR2DQSDIS Differential DQS Disable.

0 = Enable

DQS and DQS

1 = Disable DQS

11 Reserved

12 DDR2OBDIS Output Buffer Disable.

0 = Enable

1 = Disable

13 Reserved

15–14 DDR2EXTMR1 Extended Mode Register 1.

Must be set to 01.

Table A-14. DDR2CTL3 Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...