ADSP-2146x External Port Registers

A-38 ADSP-214xx SHARC Processor Hardware Reference

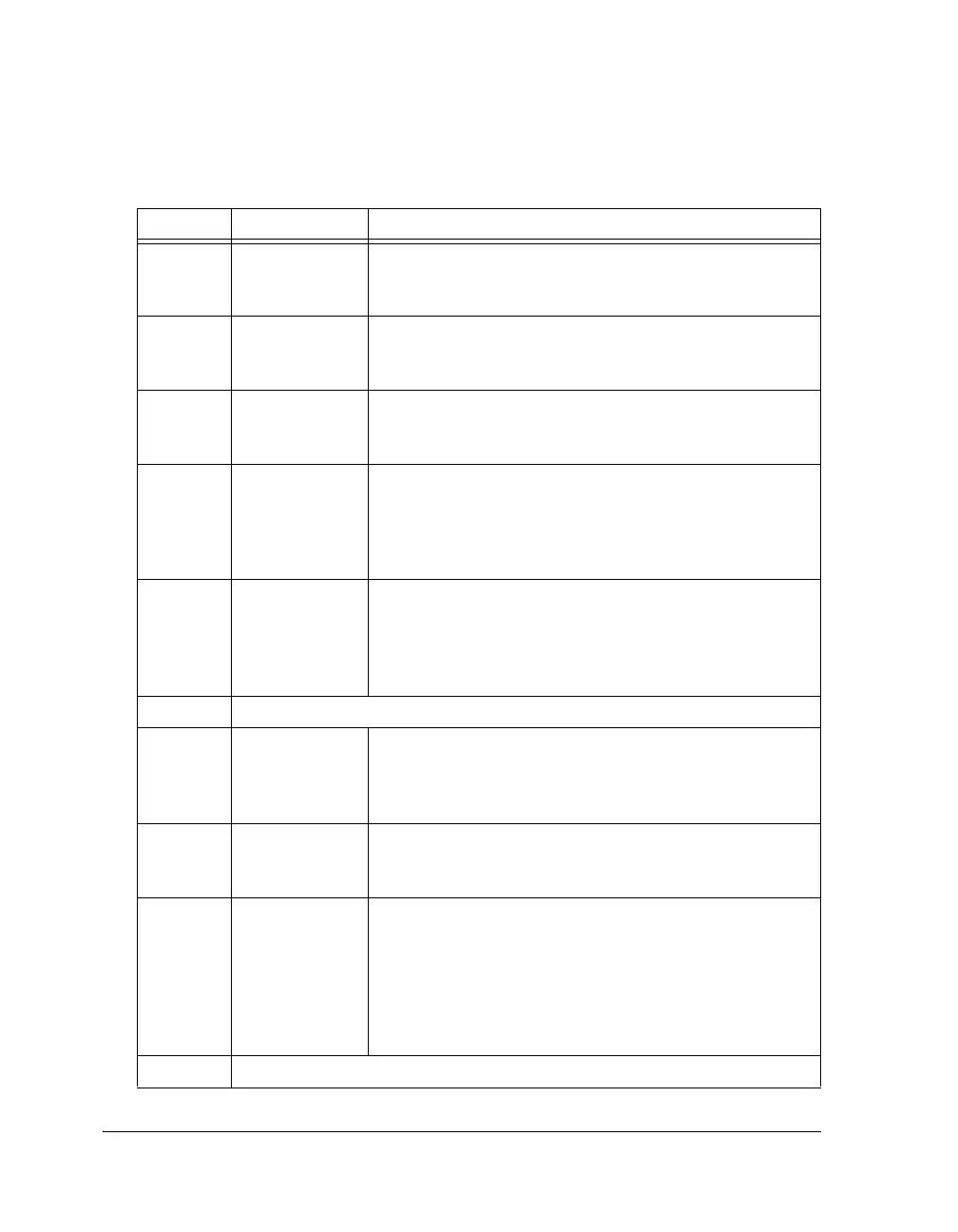

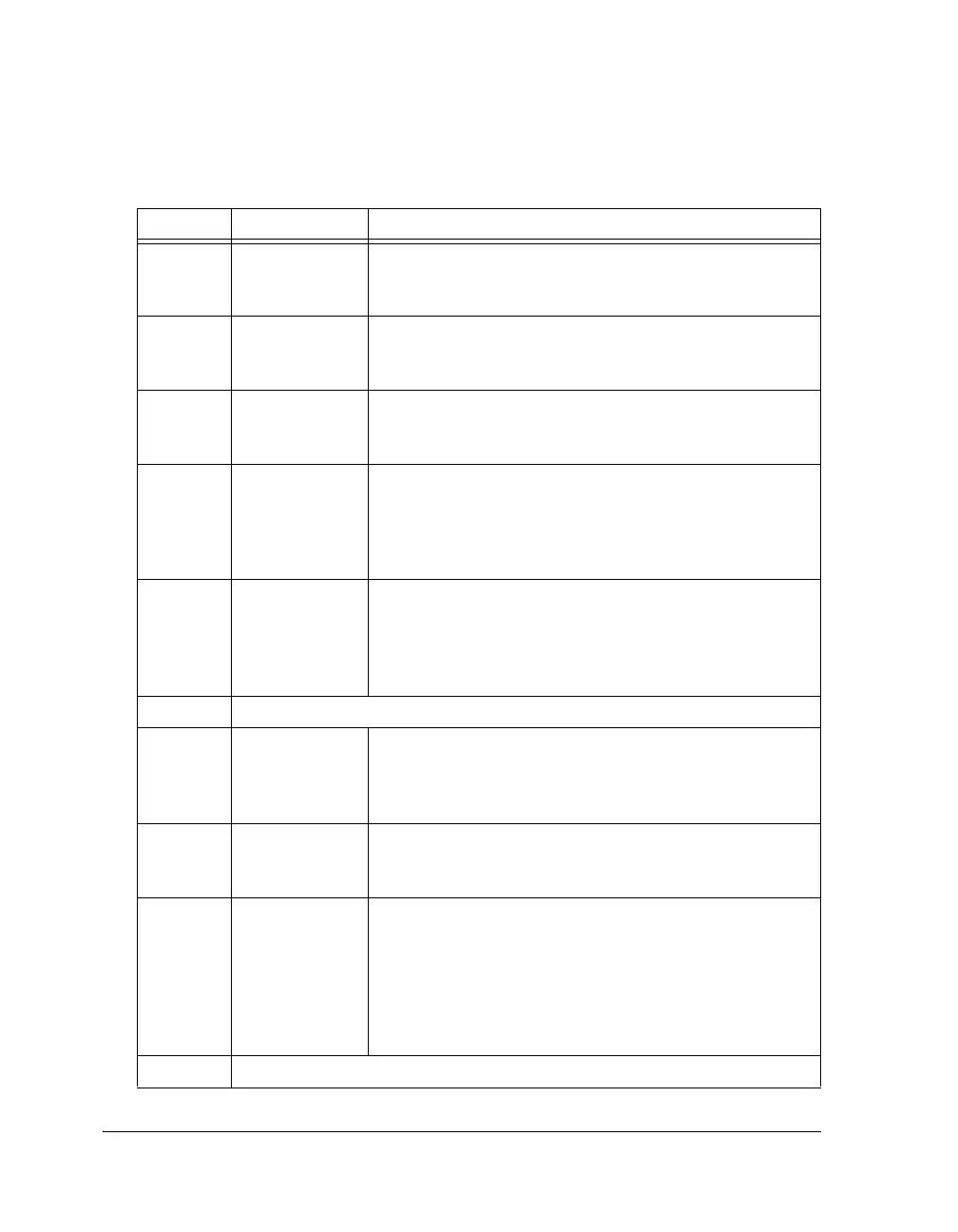

Table A-18. DDR2STAT0 Register Bit Descriptions (RO)

Bit Name Description

0 DDR2CI Controller Idle Status.

0 = Controller busy performing access or auto-refresh

1 = Controller idle

1 DDR2SRA Self-Refresh Active.

0 = Not in self-refresh mode

1 = Active

2 DDR2PUA Power-Up Sequence Active.

0 = DDR2 not in power-up

1 = DDR2 in power-up initialization sequence

3 DDR2RS DLL Reset.

0 = A power-up to DDR2 has been initialized since last DDR2

controller reset

1 = No power-up sequence occurred since last DDR2 controller

reset

4 DDR2MSE Access Error.

0 = No Error

1 = An access request to DDR2 lost because controller external

pins are in disabled state (DIS_DDCTL set)

Write a 0 to clear this bit (if set, sticky bit).

5 Reserved

6 DDR2PD Precharge Power-Down Status.

0 = Not in precharge power-down

1 = DDR2 in precharge power-down state (DIS_DDR2CKE bit

set and DDR2CKE signal deasserted)

7 DDR2DLLCAL DLL Calibration Status.

0 = Not in DLL calibration sequence

1 = DLL calibration active

8 DDR2DLLCAL

DONE

DLL Calibration Complete.

0 = A DLL calibration sequence is not happened since last

DDR2 controller reset

1 = A DLL calibration sequence occurred since last DDR2 con-

troller reset

The DLL calibration process is performed regardless of whether

an external DDR2 bank is assigned or not.

15–9 Reserved

Loading...

Loading...