Peripheral Registers

A-64 ADSP-214xx SHARC Processor Hardware Reference

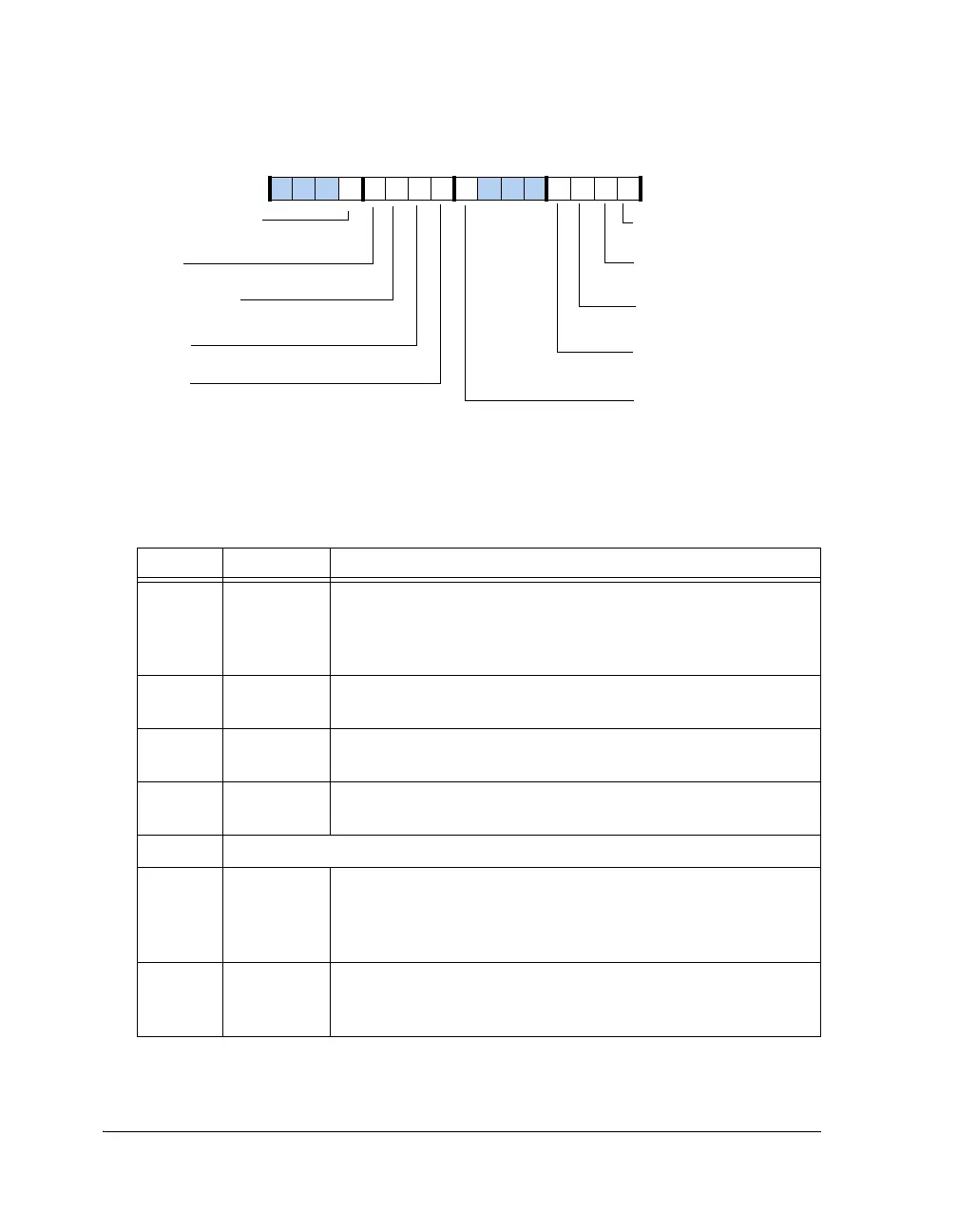

Figure A-28. LCTLx Registers

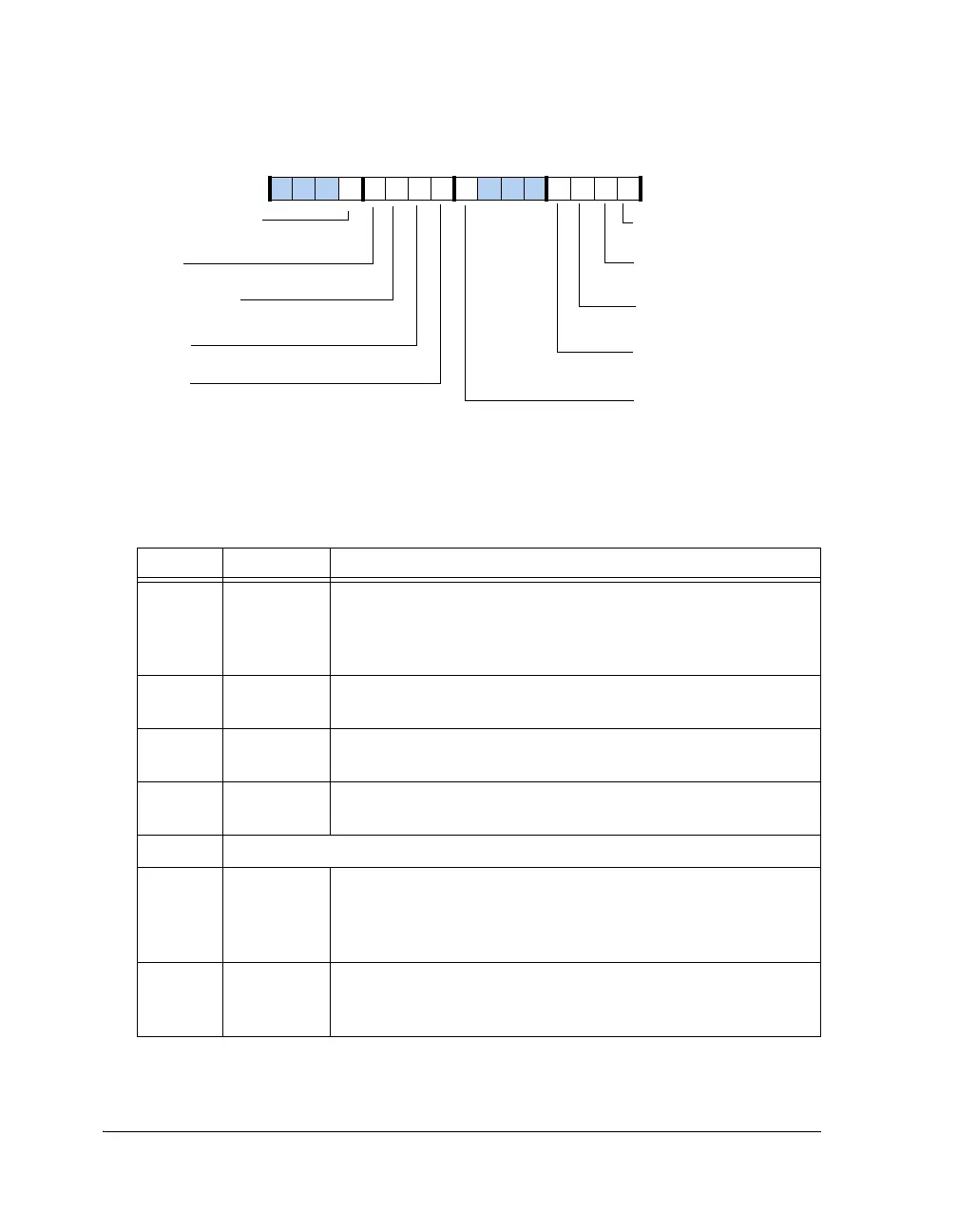

Table A-33. LCTLx Register Bit Descriptions (RW)

Bit Name Description

0LENLink Buffer Enable. Enables (if set, =1) or disables (if cleared, =0)

link buffer x (LBUFx). When the processor disables the buffer (LxEN

transitions from high to low), the processor clears the corresponding

LxSTAT and LxRERR bits.

1LDENLink Buffer DMA Enable. Enables (if set, =1) or disables (if cleared,

= 0) DMA transfers link buffer x (LBUFx).

2LCHENLink Buffer DMA Chaining Enable. Enables (if set, =1) or disables

(if cleared, =0) DMA chaining link buffer x (LBUFx).

3LTRANLink Buffer Transfer Direction. This bit selects the transfer direction

(transmit if set, =1) (receive if cleared, = 0) for link buffer x (LBUFx).

6–4 Reserved

7LP_BHDBuffer Hang Disable.

0 = Core stalls when read from empty receive or write to full transmit

buffer attempted

1 = Prevents a core hang.

8LTRQ_MSKLink Port Transmit Request Mask.

0 = Mask

1 = Unmask

LEN

LPIT_MSK

Link Buffer DMA Enable

Link Buffer Enable

LCHEN

Link Buffer DMA Chaining

Enable

LDEN

LTRAN

Link Buffer Transfer

Direction

LP_BHD

Buffer Hang Disable

Invalid Transmit Interrupt Mask

DMACH_IRPT_MSK

DMA Channel Interrupt Mask

LRRQ_MSK

Link Port Receive Request Mask

LTRQ_MSK

Link Port Transmit Request Mask

EXTTXFR_DONE_MSK

External Transfer Done Mask

09 837564 2114 12 11 101315

Loading...

Loading...