ADSP-214xx SHARC Processor Hardware Reference A-113

Registers Reference

equally by all 31 channels with four words for each channel. The buffer

depth can be up to 124 words (quadlets), when only one channel is used.

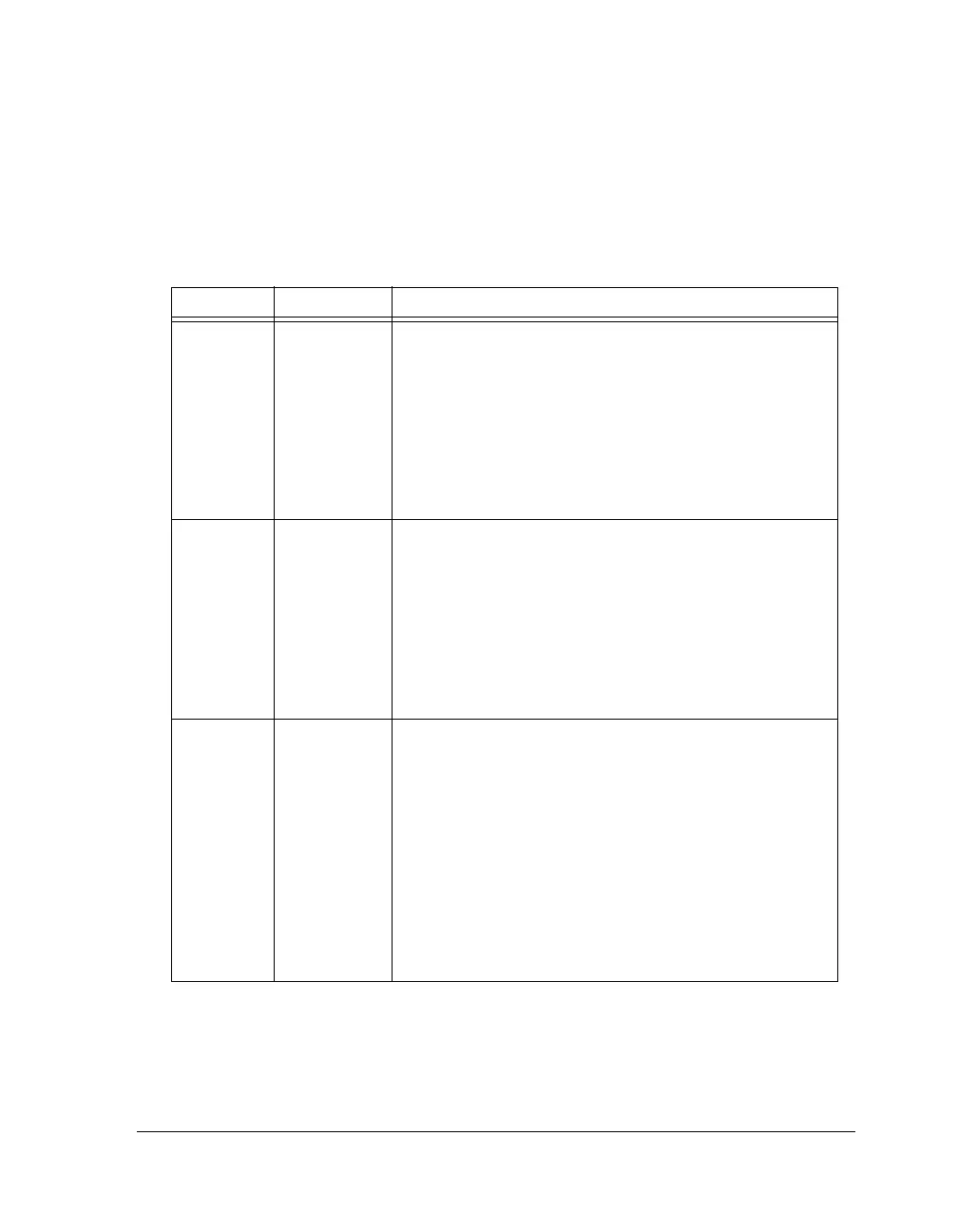

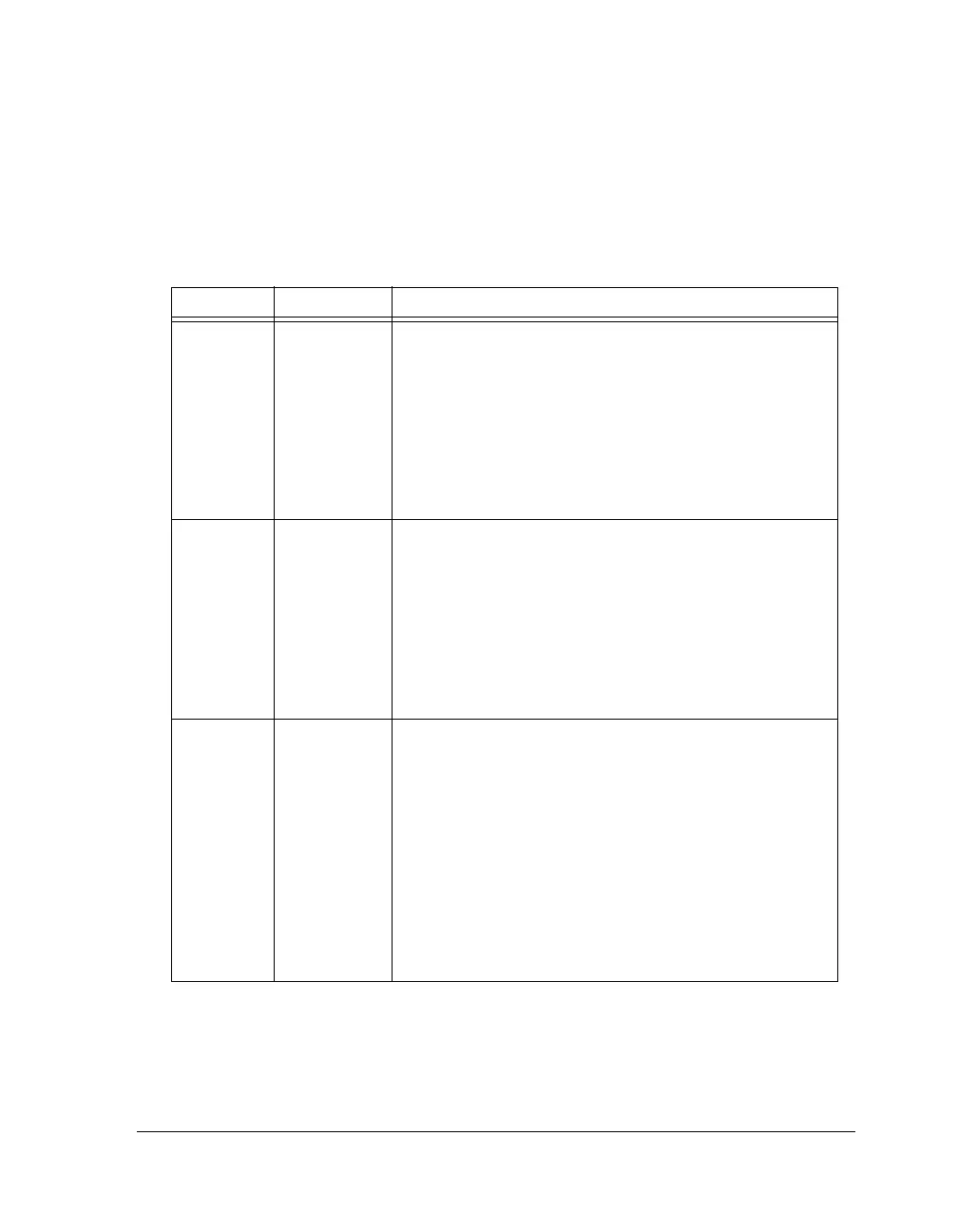

Table A-71. MLB_LCBCRx Register Description (RW)

Bit Name Description

12–0 SA Buffer Start Address. Determines the starting address (in

quadlets/4) of the channel buffer for the logical channel x.

Reset value = {120, 116, 112 …4, 0} for x = 30:0

0x0000 = start address offset of 0 words

0x0001 = start address offset of 4 words

0x0002 = start address offset of 8 words

…

0x001E = start address offset of 120 words

0x001F to 0x1FFF = Reserved

21–13 BD Buffer Depth. Defines the depth (in quadlets/4–1) of the local

channel buffer for the logical channel x.

0x000 = depth = 4 words

0x001 = depth = 8 words

0x002 = depth = 12 words

…

0x01E = depth = 124 words

0x01F to 0x1FF = Reserved

Reset value = 4 for all x=0:30

31–22 TH Buffer Threshold. Defines the threshold (in quadlets/2) of the

local channel buffer for the logical channel x in I/O mode.

Hardware uses this threshold value to determine when to issue

an I/O service request to system software.

Reset value = 2 for all x = 0:30

0x000 = threshold = 0 word

0x001 = threshold = 2 words

0x002 = threshold = 4 words

….

0x03D = threshold = 122 words

0x03E to 0x3FF = Reserved

Reserved in DMA mode

Loading...

Loading...