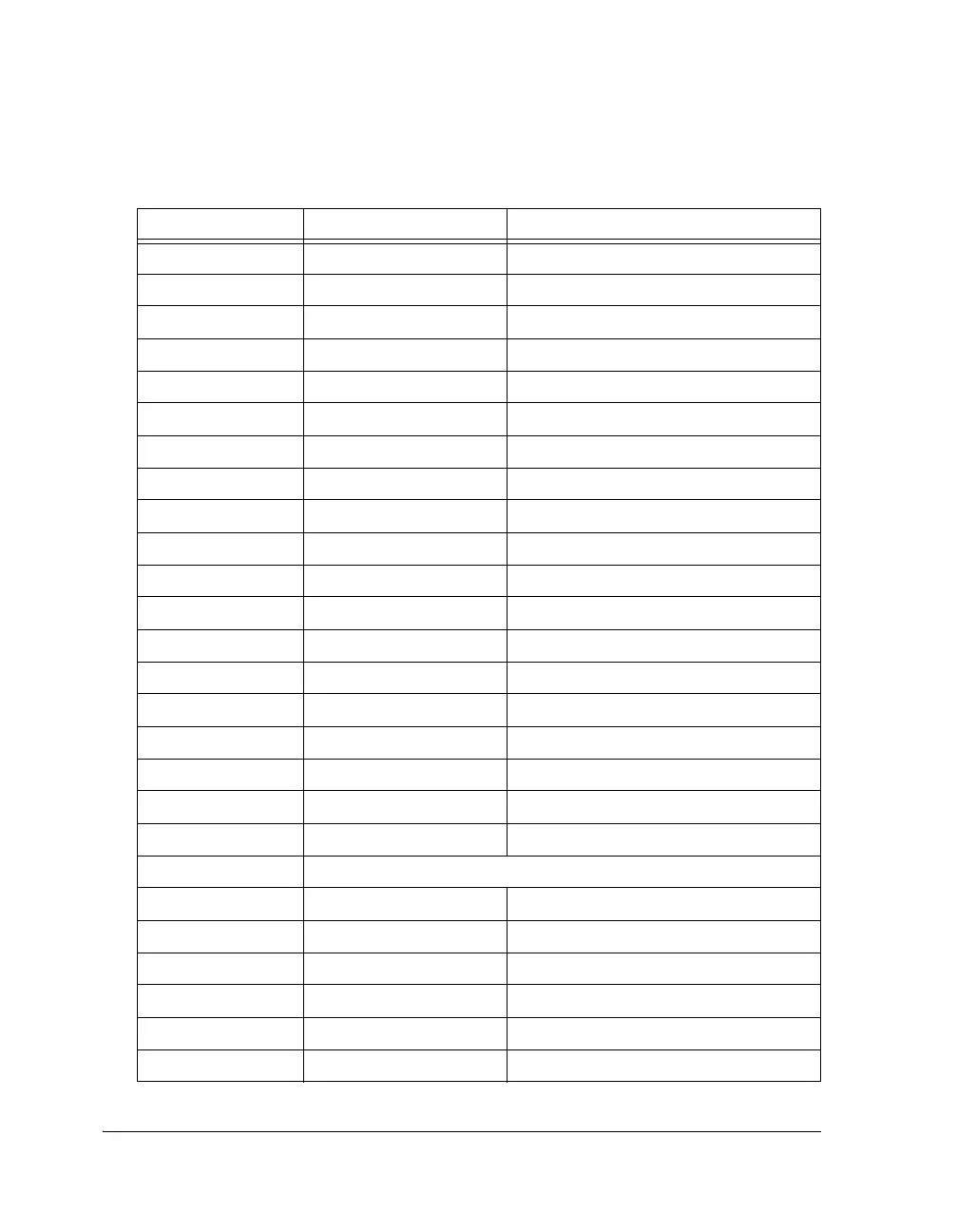

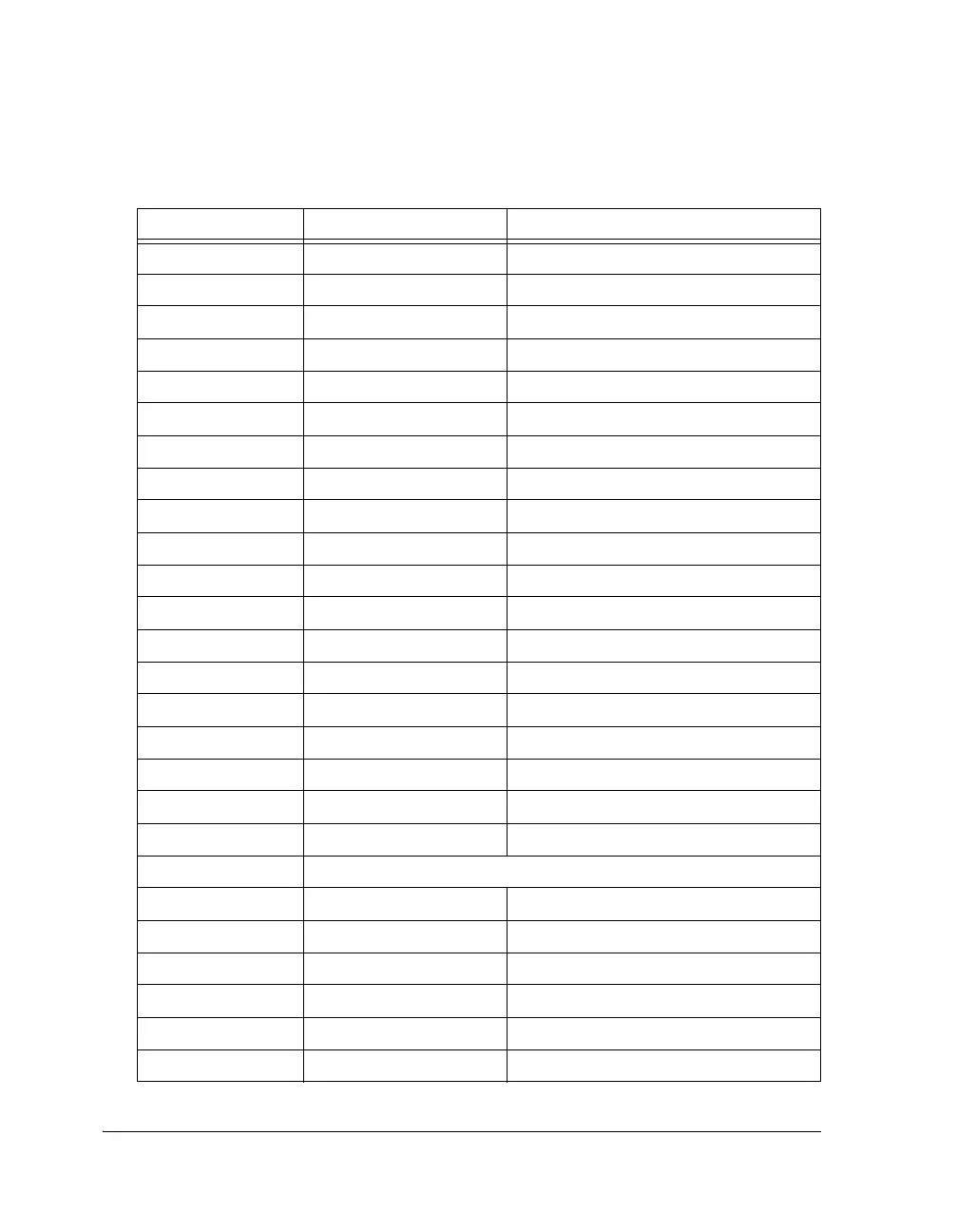

DAI Signal Routing Unit Registers

A-136 ADSP-214xx SHARC Processor Hardware Reference

0100111 (0x27) SPORT1_FS_O SPORT 1 Frame Sync

0101000 (0x28) SPORT2_FS_O SPORT 2 Frame Sync

0101001 (0x29) SPORT3_FS_O SPORT 3 Frame Sync

0101010 (0x2A) SPORT4_FS_O SPORT 4 Frame Sync

0101011 (0x2B) SPORT5_FS_O SPORT 5 Frame Sync

0101100 (0x2C) SPORT6_DA_O SPORT 6A Data

0101101 (0x2D) SPORT6_DB_O SPORT 6B Data

0101110 (0x2E) SPORT7_DA_O SPORT 7A Data

0101111 (0x2F) SPORT7_DB_O SPORT 7B Data

0110000 (0x30) PDAP_STRB_O PDAP Data Transfer Request Strobe

0110001 (0x31) DIT_BLKSTART_O S/PDIF TX Block Start Output

0110100 (0x34) SPORT6_CLK_O SPORT 6 Clock

0110101 (0x35) SPORT7_CLK_O SPORT 7 Clock

0110110 (0x36) SPORT6_FS_O SPORT 6 Frame Sync

0110111 (0x37) SPORT7_FS_O SPORT 7 Frame Sync

0111000 (0x38) PCG_CLKA_O Precision Clock A

0111001 (0x39) PCG_CLKB_O Precision Clock B

0111010 (0x3A) PCG_FSA_O Precision Frame Sync A

0111011 (0x3B) PCG_FSB_O Precision Frame Sync B

0111100 (0x3C) Reserved

0111101 (0x3D) SRC0_DAT_OP_O SRC0 Data Output

0111110 (0x3E) SRC1_DAT_OP_O SRC1 Data Output

0111111 (0x3F) SRC2_DAT_OP_O SRC2 Data Output

1000000 (0x40) SRC3_DAT_OP_O SRC3 Data Output

1000001 (0x41) DIR_DAT_O SPDIF_RX Data Output

1000010 (0x42) DIR_FS_O SPDIF_RX Frame Sync Output

Table A-78. Group D Sources – Pin Signal Assignments (Cont’d)

Selection Code Source Signal Description (Source Selection)

Loading...

Loading...