ADSP-214xx SHARC Processor Hardware Reference A-197

Registers Reference

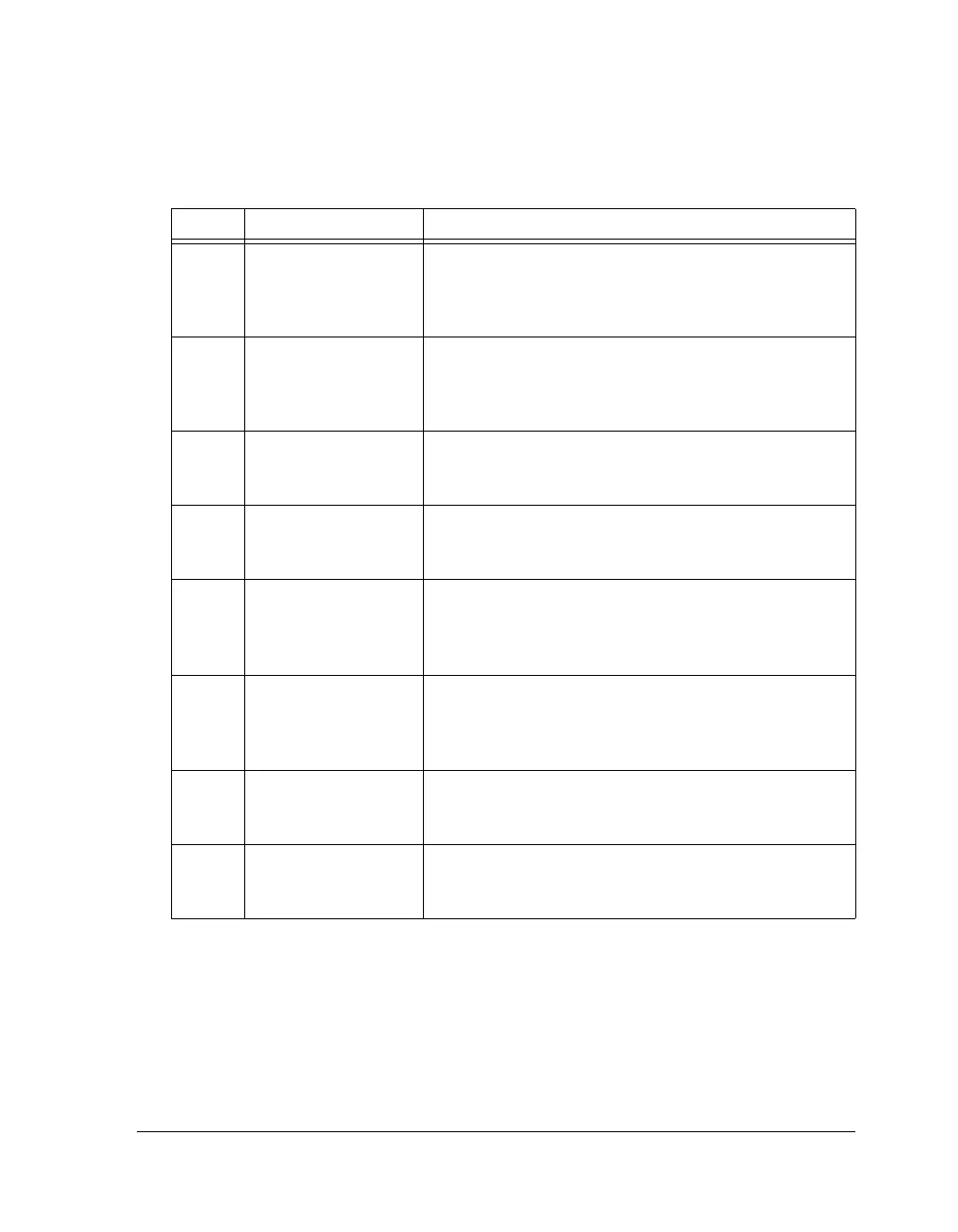

Table A-102. PCG_SYNC1 Register Bit Descriptions (RW)

Bit Name Description

0FSA_SYNC Enable Synchronization of Frame Sync A With External

Frame Sync.

0 = Frame sync disabled

1 = Frame sync enabled

1CLKA_SYNC Enable Synchronization of Clock A With External Frame

Sync.

0 = Clock disabled

1 = Clock enabled

2CLKA_SOURCE_IOPEnable Clock A Input Source.

0 = Output selected by CLKASOURCE bit

1 = PCLK selected for clock A.

3FSA_SOURCE_IOPEnable Frame Sync A Input Source.

0 = Output selected by FSASOURCE bit

1 = PCLK selected for frame sync A.

16 FSB_SYNC Enable Synchronization of Frame Sync B With External

Frame Sync.

0 = Frame sync disabled

1 = Frame sync enabled

17 CLKB_SYNC Enable Synchronization of Clock B With External Frame

Sync.

0 = Clock disabled

1 = Clock enabled

18 CLKB_SOURCE_IOP EnabLe Clock B Input Source.

0 = Output selected by CLKBSOURCE bit

1 = PCLK selected for clock B.

19 FSB_SOURCE_IOP Enable Frame Sync B Input Source.

0 = Output selected by FSBSOURCE bit

1 = PCLK selected for frame sync B.

Loading...

Loading...