ADSP-214xx SHARC Processor Hardware Reference A-201

Registers Reference

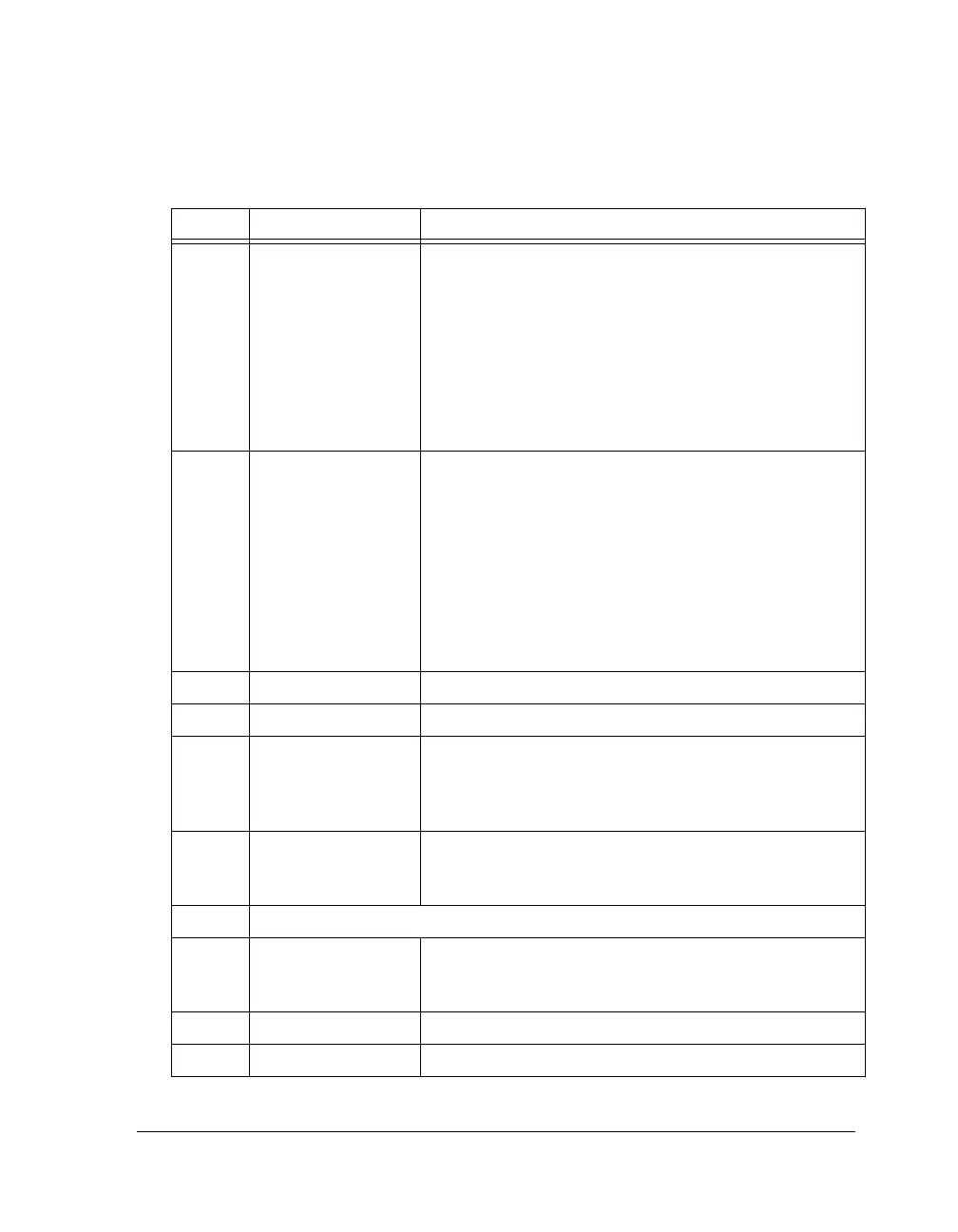

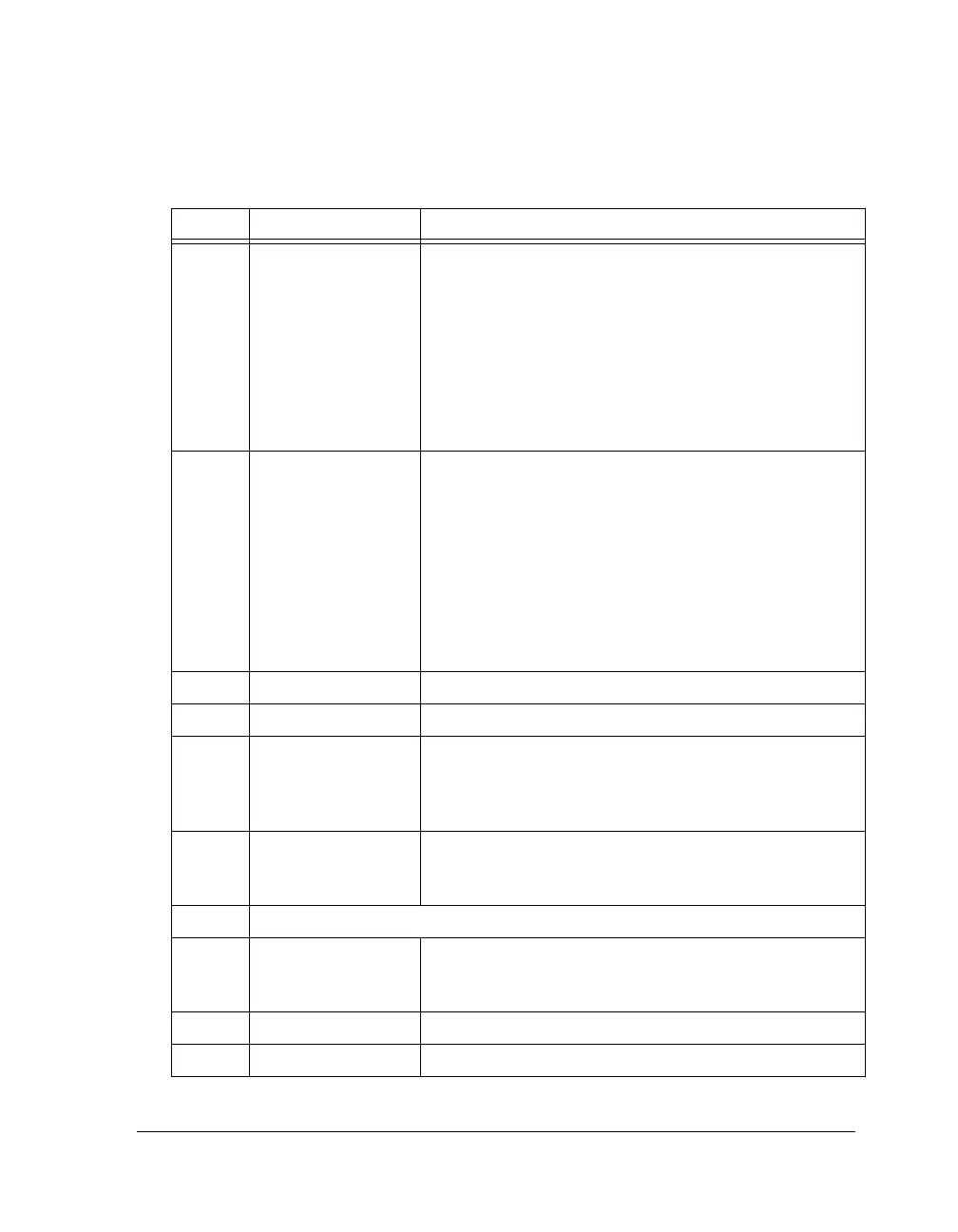

8–6 DIT_SMODEIN Serial Data Input Format. Selects the input format as follows:

000 = Left-justified

001 = I

2

S

010 = Reserved

011 = Reserved

100 = Right-justified, 24-bits

101 = Right-justified, 20-bits

110 = Right-justified, 18-bits

111 = Right-justified, 16-bits

9DIT_AUTO Automatically Generate Block Start. Automatically generate

block start. When enabled, the transmitter is in standalone

mode where it inserts block start, channel status, and validity

bits on its own. If the channel status or validity buffer needs to

be enabled (after the SRU programming is complete), first

write to the buffers with the required data and then enable the

buffers by setting the DIT_AUTO bit.

0 = Manually start block transfer according to input stream

status bits

1 = Automatically start block transfer.

10 DIT_VALIDL Validity Bit A. Use with channel status buffer.

11 DIT_VALIDR Validity Bit B. Use with channel status buffer.

12 (RO) DIT_BLKSTART Block Start. Status bit that indicates block start (when bit 9,

DIT_AUTO = 1).

0 = Current word is not block start

1 = Current word is block start

13 (RO) DIT_USRPEND User Bits Pending. This bit is set if the update of the internal

buffer from the DITUSRBITA/Bx registers has not completed

yet.

14 Reserved

15 EXT_SYNC_EN External Sync Enable. When set (Regardless of bit 9) the inter-

nal frame counter is set to zero at an internal LRCLK rising

edge followed by an DIT_EXTSYNC_I rising edge.

23–16 DIT_B0CHANL Channel Status Byte 0 for Subframe A.

31–24 DIT_B0CHANR Channel Status Byte 0 for Subframe B.

Table A-104. DITCTL Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...