DPI Signal Routing Unit Registers

A-224 ADSP-214xx SHARC Processor Hardware Reference

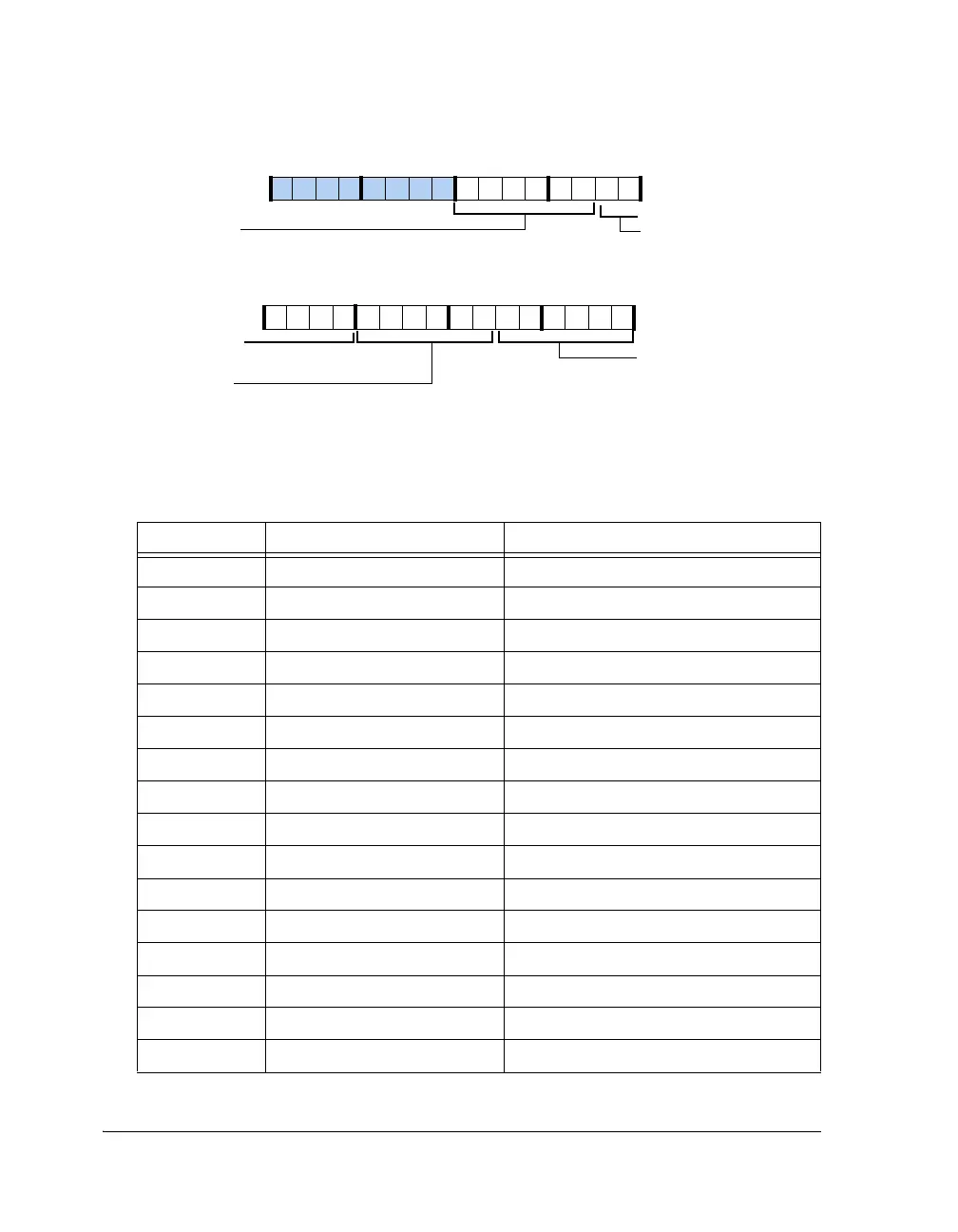

Figure A-126. SRU2_PIN2 Register

Table A-119. Group B Signals

Binary Signal Description (Source Selection)

000000 (0x0) LOW Logic Level Low (0)

000001 (0x1) HIGH Logic Level High (1)

000010 (0x2) DPI_PB01_O External Pin 1

000011 (0x3) DPI_PB02_O External Pin 2

000100 (0x4) DPI_PB03_O External Pin 3

000101 (0x5) DPI_PB04_O External Pin 4

000110 (0x6) DPI_PB05_O External Pin 5

000111 (0x7) DPI_PB06_O External Pin 6

001000 (0x8) DPI_PB07_O External Pin 7

001001 (0x9) DPI_PB08_O External Pin 8

001010 (0xA) DPI_PB09_O External Pin 9

001011 (0xB) DPI_PB10_O External Pin 10

001100 (0xC) DPI_PB11_O External Pin 11

001101 (0xD) DPI_PB12_O External Pin 12

001110 (0xE) DPI_PB13_O External Pin 13

001111 (0xF) DPI_PB14_O External Pin 14

DPI Pin Buffer 13 Input

DPI_PB14_I (23–18 )

DPI Pin Buffer 14 Input

DPI_PB13_I (17–12)

DPI_PB12_I (11–6)

DPI Pin Buffer 12 Input

DPI_PB11_I (5–0)

DPI Pin Buffer 11 Input

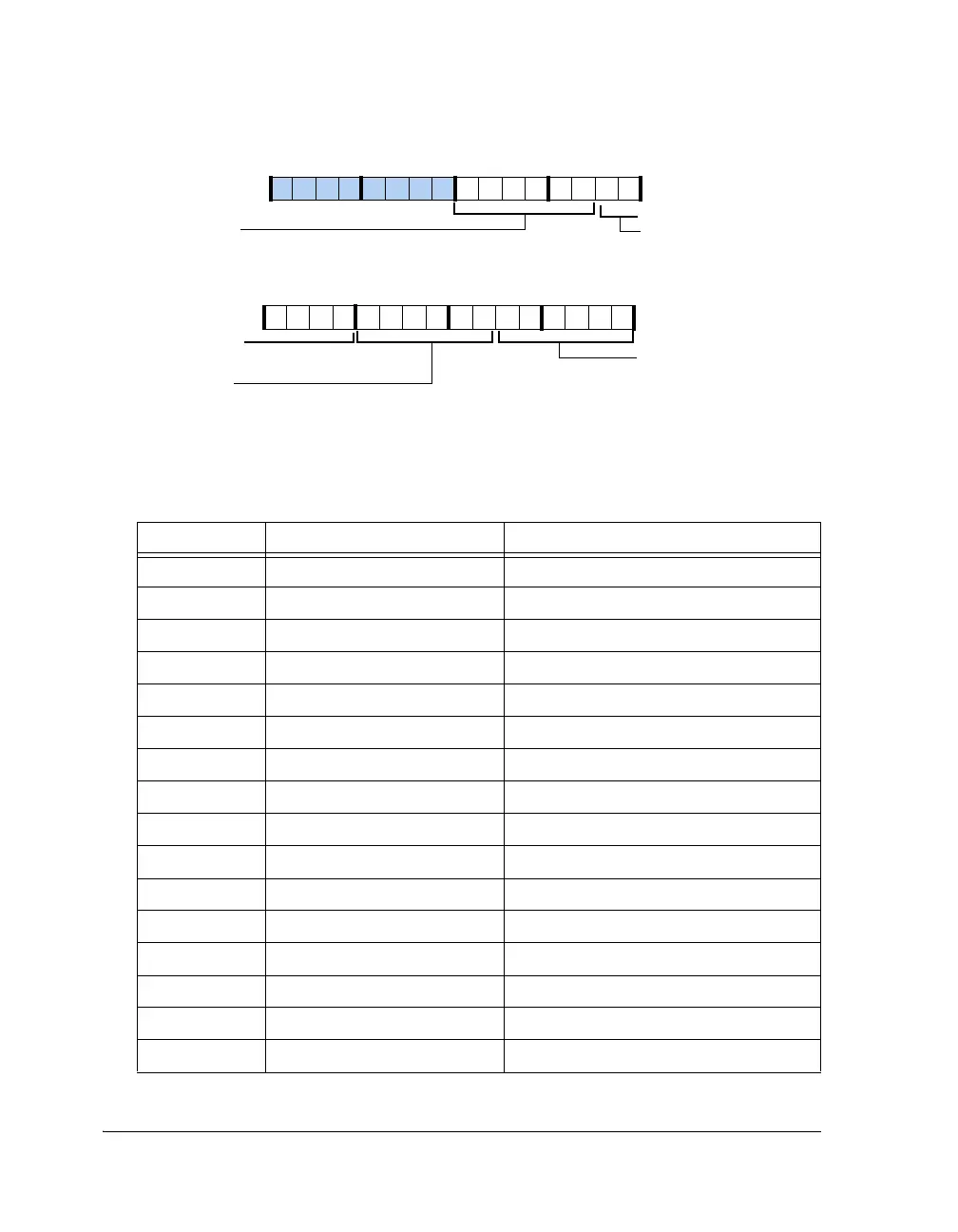

DPI Pin Buffer 13 Input

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

DPI_PB13_I (17–12) con’t

Loading...

Loading...