ADSP-214xx SHARC Processor Hardware Reference 3-9

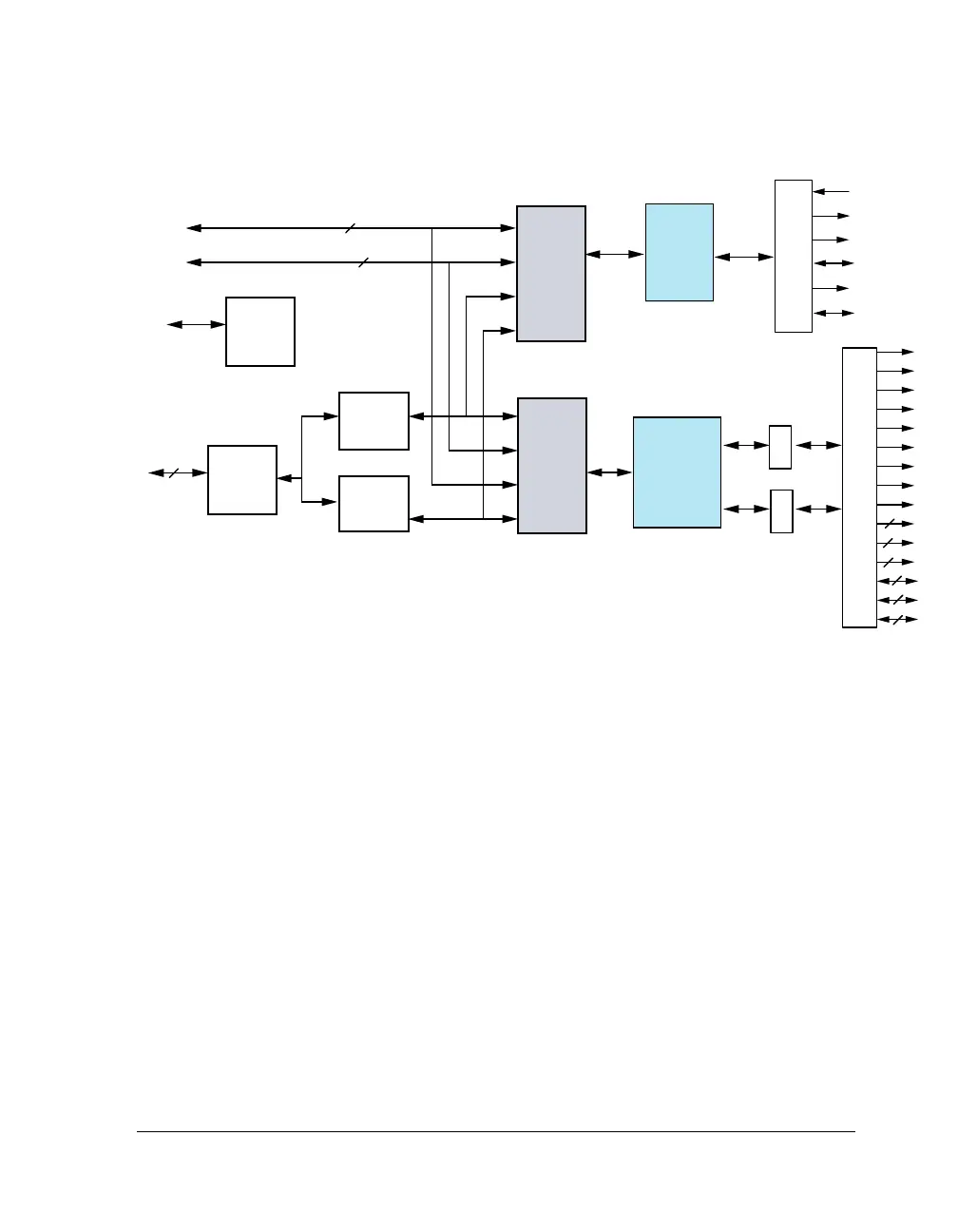

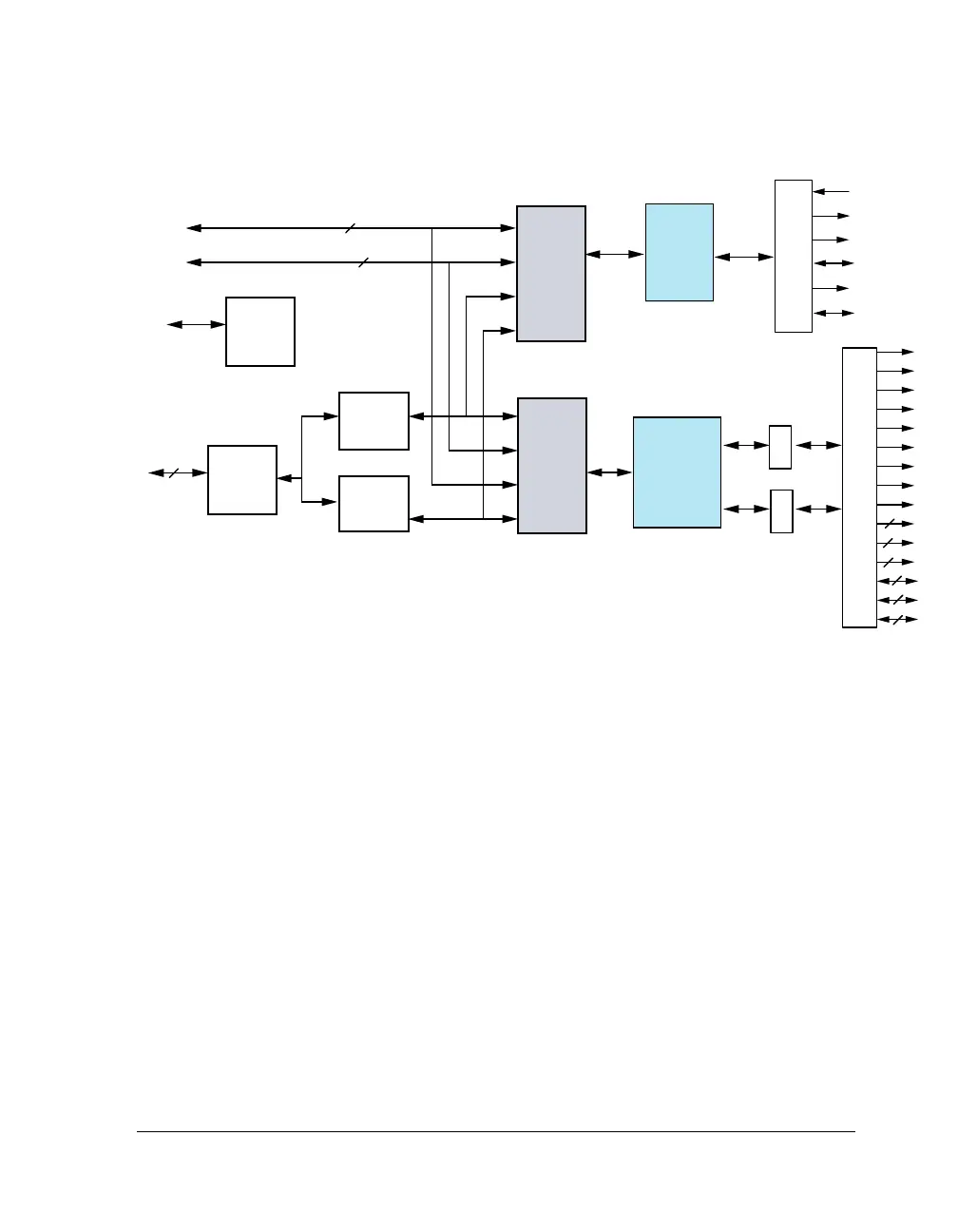

External Port

The external port uses a three stage arbitration process whereby all DMA

requests need to pass through the first stage until one request wins. When

this occurs, the winning DMA channel needs to arbitrate with a SPORT

DMA group (for example group A has four DMA channels SP1A/B,

SP0A/B). The winning DMA channel then has a last arbitration process

with the core where the following occurs.

1. External port DMA channels 0/1 rotating priority or high/low

priorities.

2. Winning DMA channel arbitrating with SPORT DMA groups.

3. Winning DMA channel arbitrating with core access.

In the EPCTL register, the EBPR and DMAPR bits define the priorities. All the

bits of

EPCTL register can be changed only when the external port is idle

Figure 3-2. External Port Functional Block Diagram (DDR2)

DDR2

CONTROLLER

ACK

AMI_WR

AMI_RD

AMI_MS

AMI_ADDR

AMI_DATA

DLL1DLL0

AMI

AMI PADS

DDR2 PADS

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2_

DDR2

DDR2_

4

2

19

2

2

16

DMA

ARBITER

DMA

0

DMA

1

DDR2

ARBITER

EP CORE BUS

IOD1 (EP)

DMA BUS

32

64

EP IOP

REGISTER

PERIPHERAL

CORE BUS

SPEP (SPORT) BUS

AMI

ARBITER

32

Loading...

Loading...