DDR2 DRAM Controller (ADSP-2146x)

3-64 ADSP-214xx SHARC Processor Hardware Reference

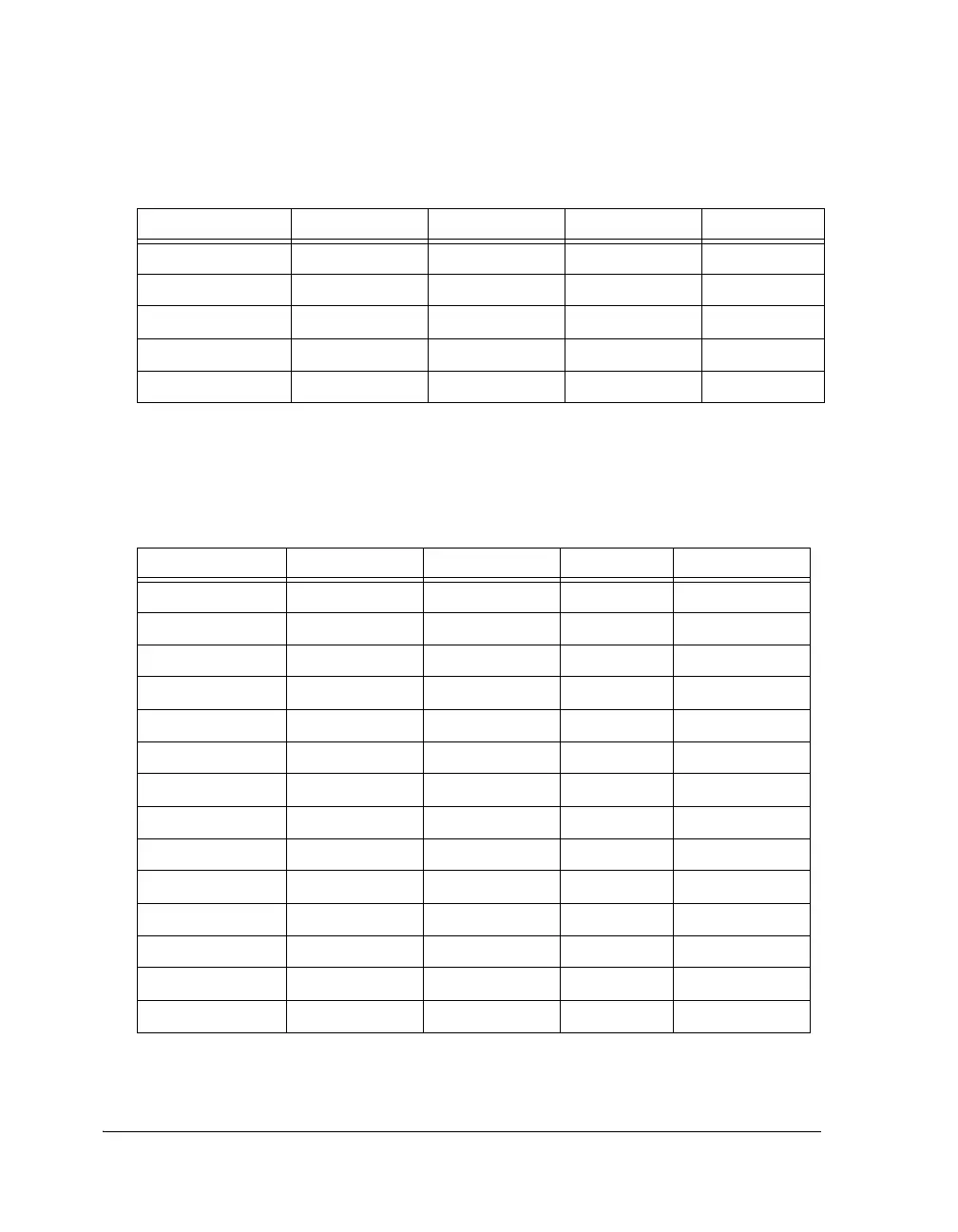

Table 3-12 shows

DDR2ADDRMODE = 0, DDR2RAW = 100 (12), DDR2CAW = 11

(11), DDR2BC = 01(four banks).

DDR2_ADDR[4] IA[3] IA[16] A[4]

DDR2_ADDR[3] IA[2] IA[15] A[3]

DDR2_ADDR[2] IA[1] IA[14] A[2]

DDR2_ADDR[1] IA[0] IA[13] A[1]

DDR2_ADDR[0] 1/0 IA[12] A[0]

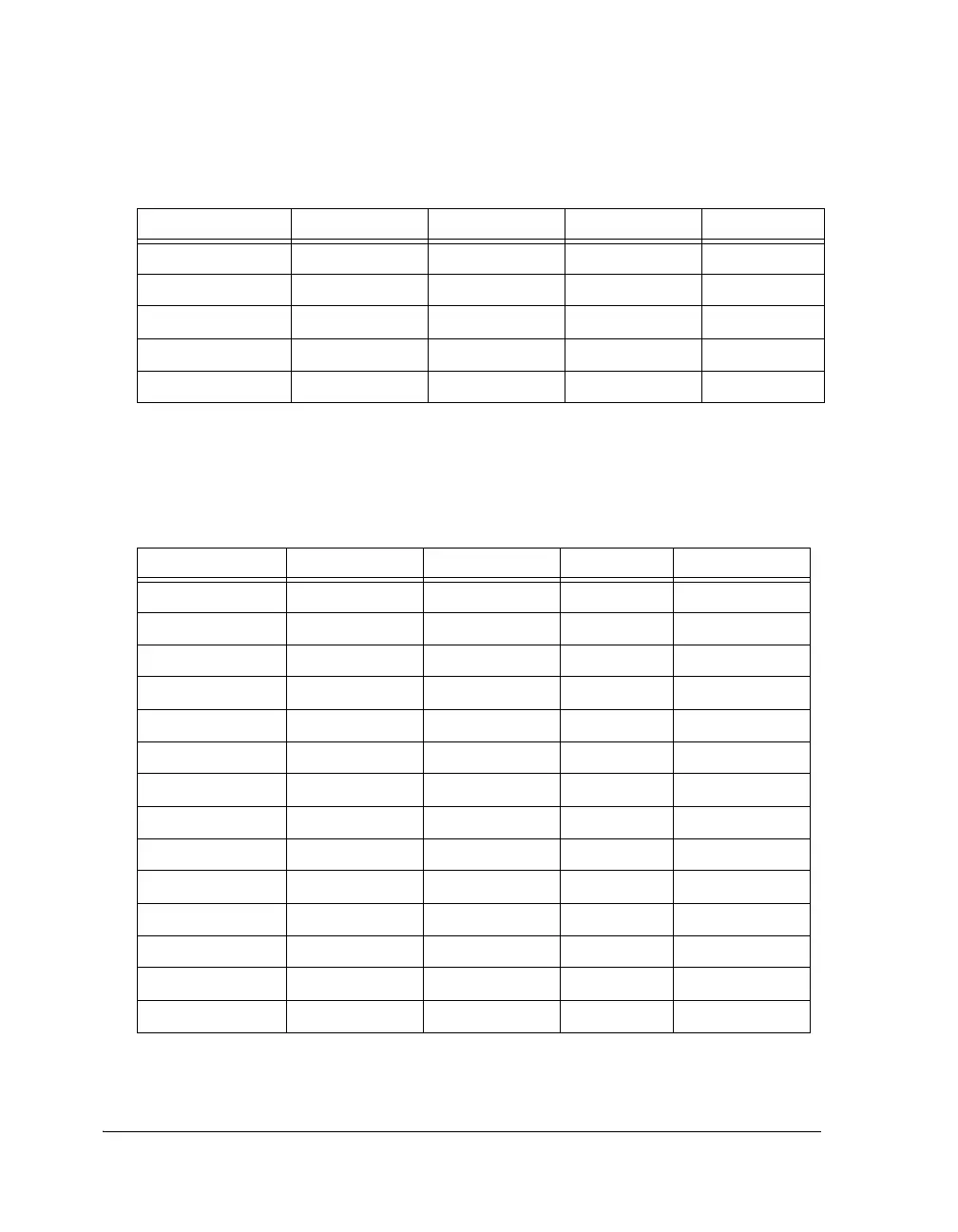

Table 3-13. 16-bit Address Mapping (4 Banks, Page Interleaving)

SHARC Pin Column Address Row Address Bank Address DDR2 Pin

DDR2_BA1 IA[11] BA[1]

DDR2_BA0 IA[10] BA[0]

DDR2_ADDR[13]

DDR2_ADDR[12] A[12]

DDR2_ADDR[11] IA[9] IA[23] A[11]

DDR2_ADDR[10] IA[22] A[10]

DDR2_ADDR[9] IA[8] IA[21] A[9]

DDR2_ADDR[8] IA[7] IA[20] A[8]

DDR2_ADDR[7] IA[6] IA[19] A[7]

DDR2_ADDR[6] IA[5] IA[18] A[6]

DDR2_ADDR[5] IA[4] IA[17] A[5]

DDR2_ADDR[4] IA[3] IA[16] A[4]

DDR2_ADDR[3] IA[2] IA[15] A[3]

DDR2_ADDR[2] IA[1] IA[14] A[2]

Table 3-12. 16-bit Address Mapping (8 Banks, Page Interleaving) (Cont’d)

SHARC Pin Column Address Row Address Bank Address DDR2 Pin

Loading...

Loading...