ADSP-214xx SHARC Processor Hardware Reference 9-41

Digital Application/Digital Peripheral Interfaces

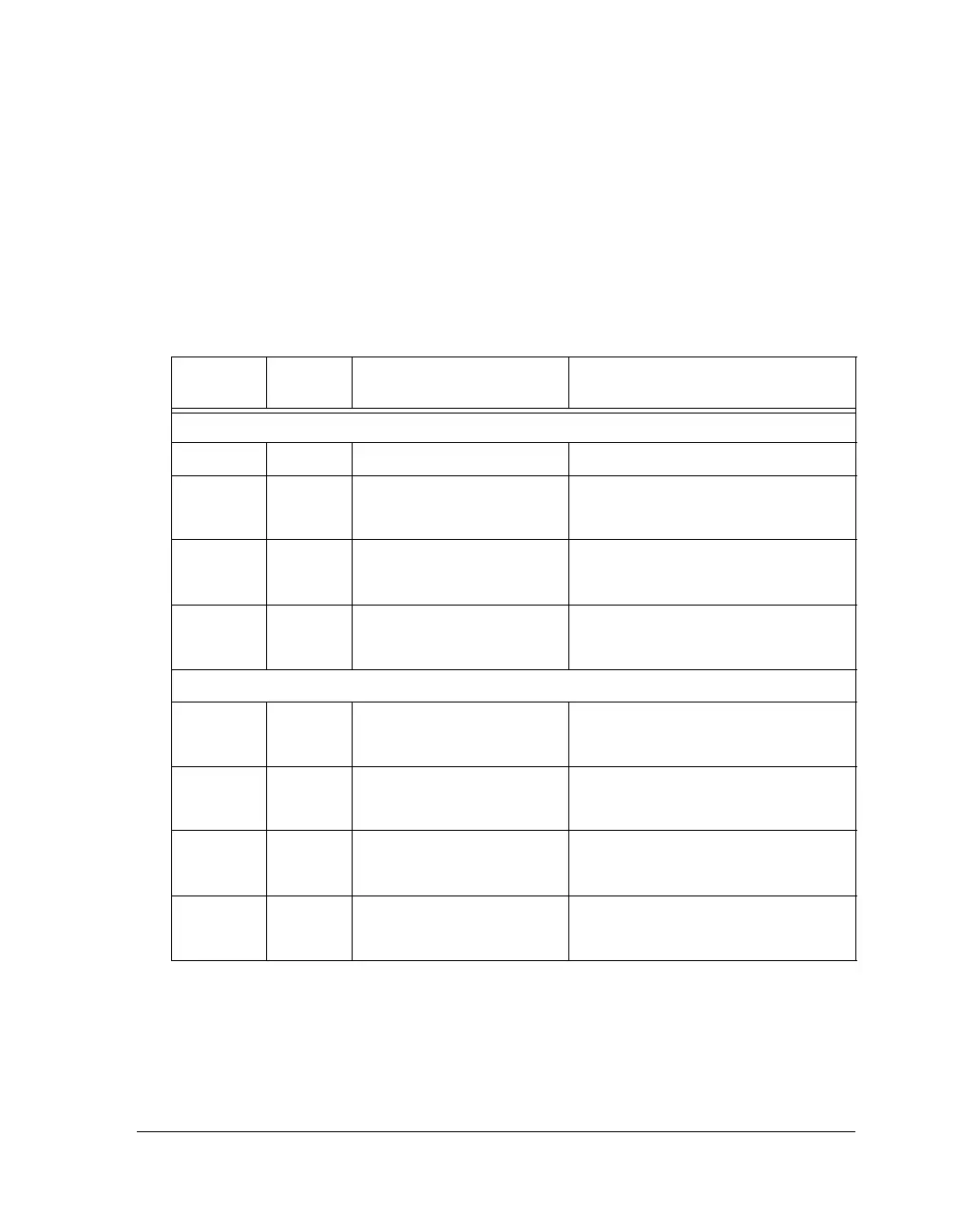

The SRU can be used for this purpose. Table 9-9 describes the different

possible routings based on the peripheral.

The peripheral’s loop back mode for debug is independent from

both of the signal routing units.

Table 9-9. Loop Back Routing

Peripheral Loopback

Mode

SRU/SRU2 Internal Routing

for Loopback

SRU/SRU2 External Routing for

Loopback

DAI

IDP N/A N/A N/A

SPORT Yes

SPORTx_xx_O

→

SPORTx_xx_I

SPORTx_xx_O → DAI_PBxx_I

DAI_PBxx_O

→ SPORTx_xx_I

S/PDIF

Tx/Rx

No

DIT_O → DIR_I DIT_O → DAI_PBxx_I

DAI_PBxx_O → DIR_I

SRC No

SRCx_DAT_OP_O →

SRCx_DAT_IP_I

SRCx_DAT_OP_O → DAI_PBxx_I

DAI_PBxx_O

→ SRCx_DAT_IP_I

DPI

Timer No

TIMERx_O

→ TIMERx_I TIMERx_O → DPI_PBxx_I

DPI_PBxx_O

→ TIMERx_I

SPI Yes No

SPIx_xx_O

→ DPI_PBxx_I

DPI_PBxx_O

→ SPIx_xx_I

UART0 No

UART0_TX_O →

UART0_RX_I

UART0_TX_O → DPI_PBxx_I

DPI_PBxx_O

→ UART0_RX_I

TWI No No

TWI_xx_O → DPI_PBxx_I

DPI_PBxx_O

→ TWI_xx_I

Loading...

Loading...