Pin Descriptions

11-4 ADSP-214xx SHARC Processor Hardware Reference

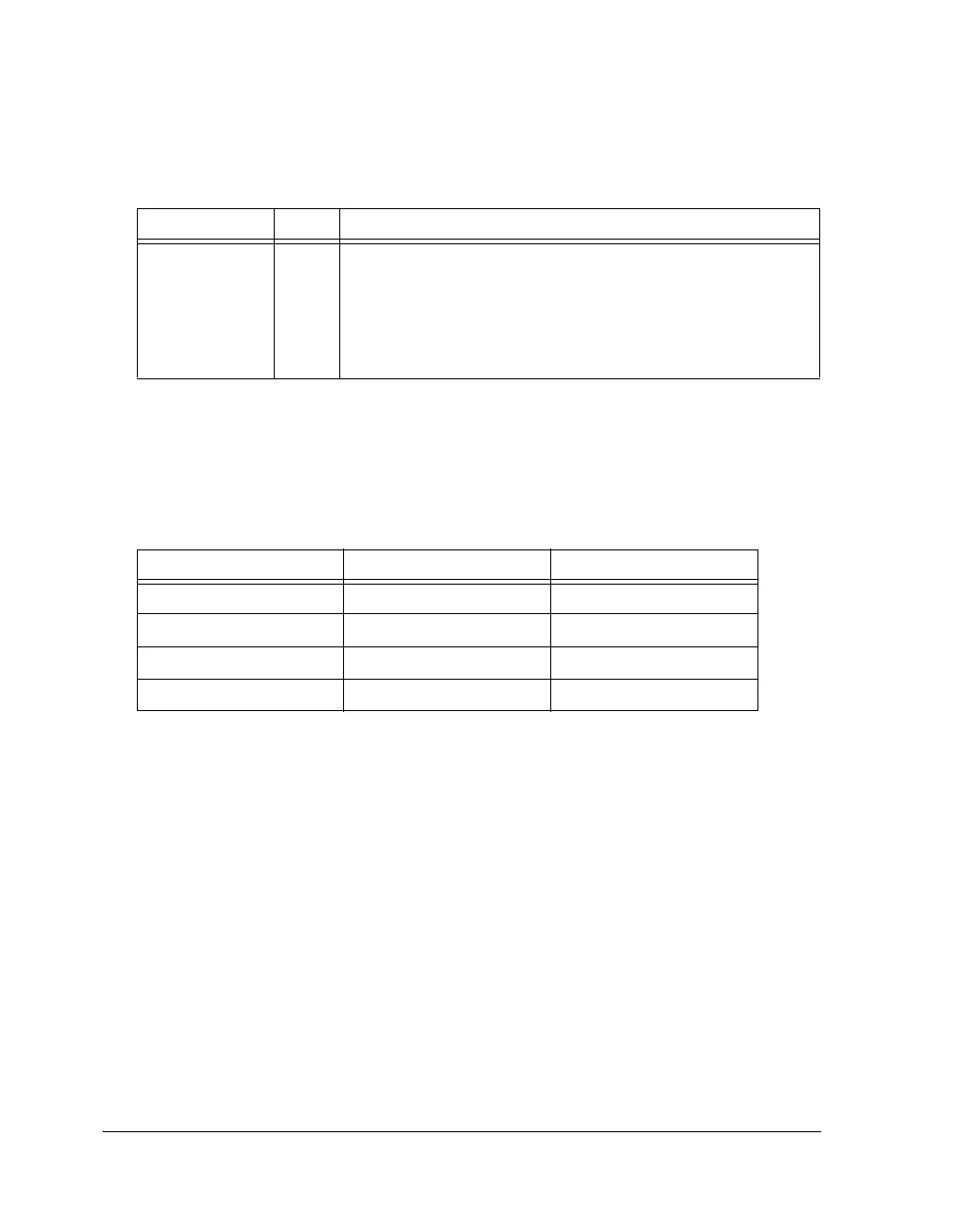

Table 11-4 provides descriptions of the pin multiplexing between DAI

and external port. For more information, see “Pin Multiplexing” on

page 23-28.

PDAP_STRB_O O Parallel Data Acquisition Port Clock input. The PDAP packing

unit asserts the output strobe whenever there is 32-bit data available

for transfer to the IDP FIFO. The width of this pulse is equal to 2 x

PCLK cycles. This signal can be used to synchronize external

requests for new PDAP data. Note that input has multiplexed con-

trol.

Table 11-4. Pin Multiplexing between DAI and External Port

Signal DAI External Port

Serial Clock IDP0_CLK_I DATA[10]

Frame Sync IDP0_FS_I DATA[11]

Data DAI_PB20–1 DATA[31–12]

Strobe Out PDAP_STRB_O DATA[8]

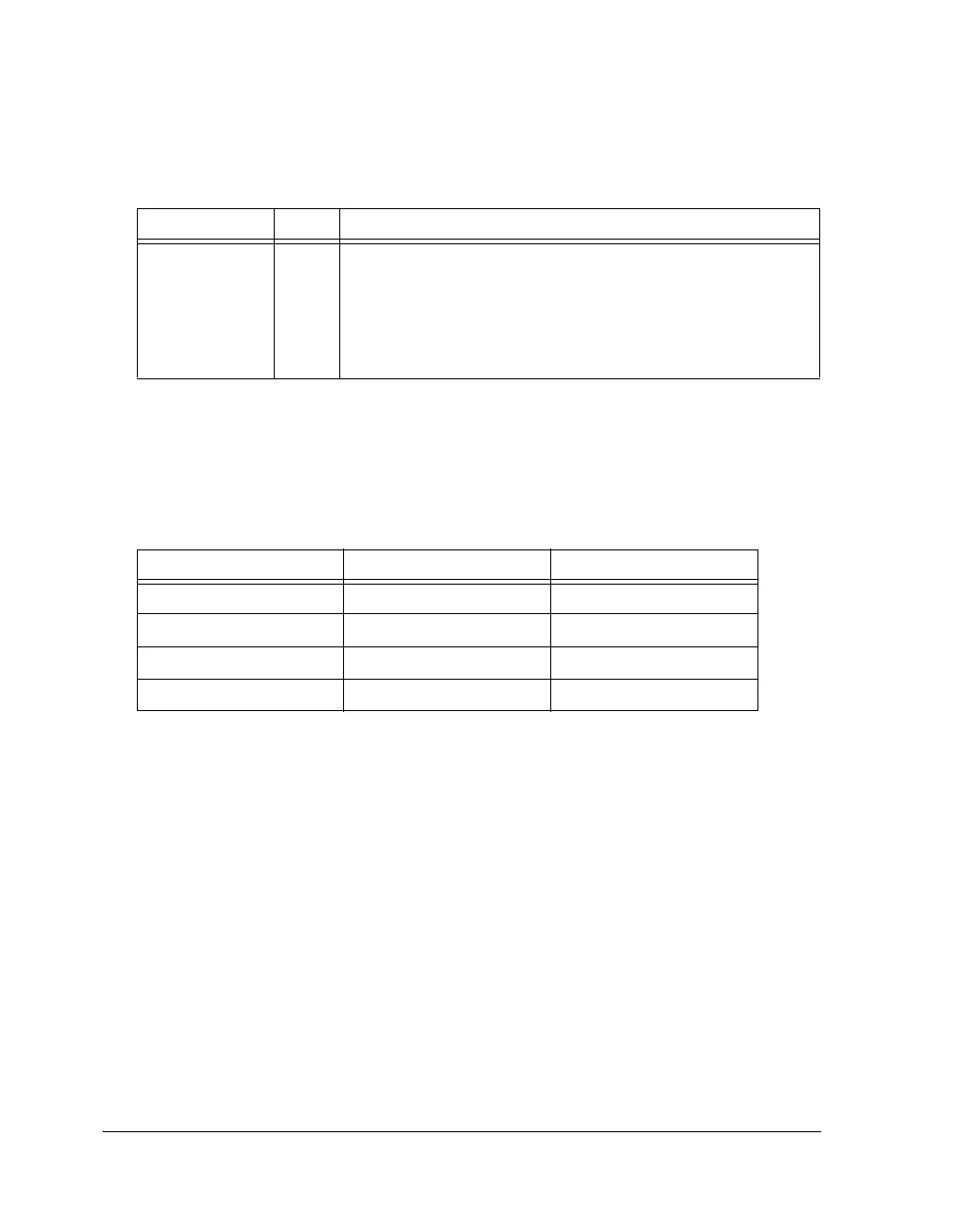

Table 11-3. PDAP Pin Descriptions (Cont’d)

Internal Nodes Type Description

Loading...

Loading...