ADSP-214xx SHARC Processor Hardware Reference 11-7

Input Data Port

The parallel data is acquired through the parallel data acquisition port

(PDAP) which provides a means of moving high bandwidth data to the

core’s memory space. The data may be sent to memory as one 32-bit word

per input clock cycle or packed together (for up to four clock cycles worth

of data).

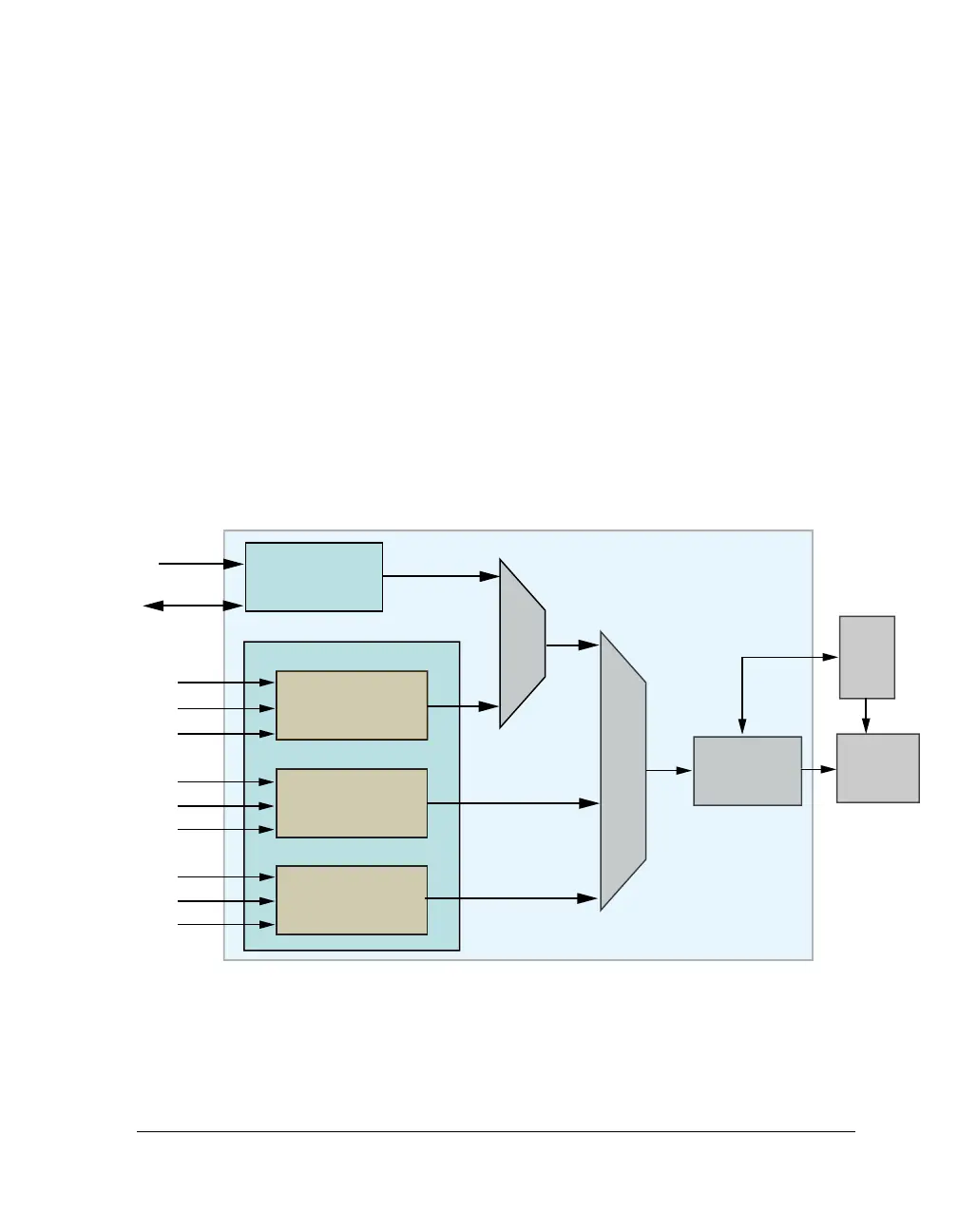

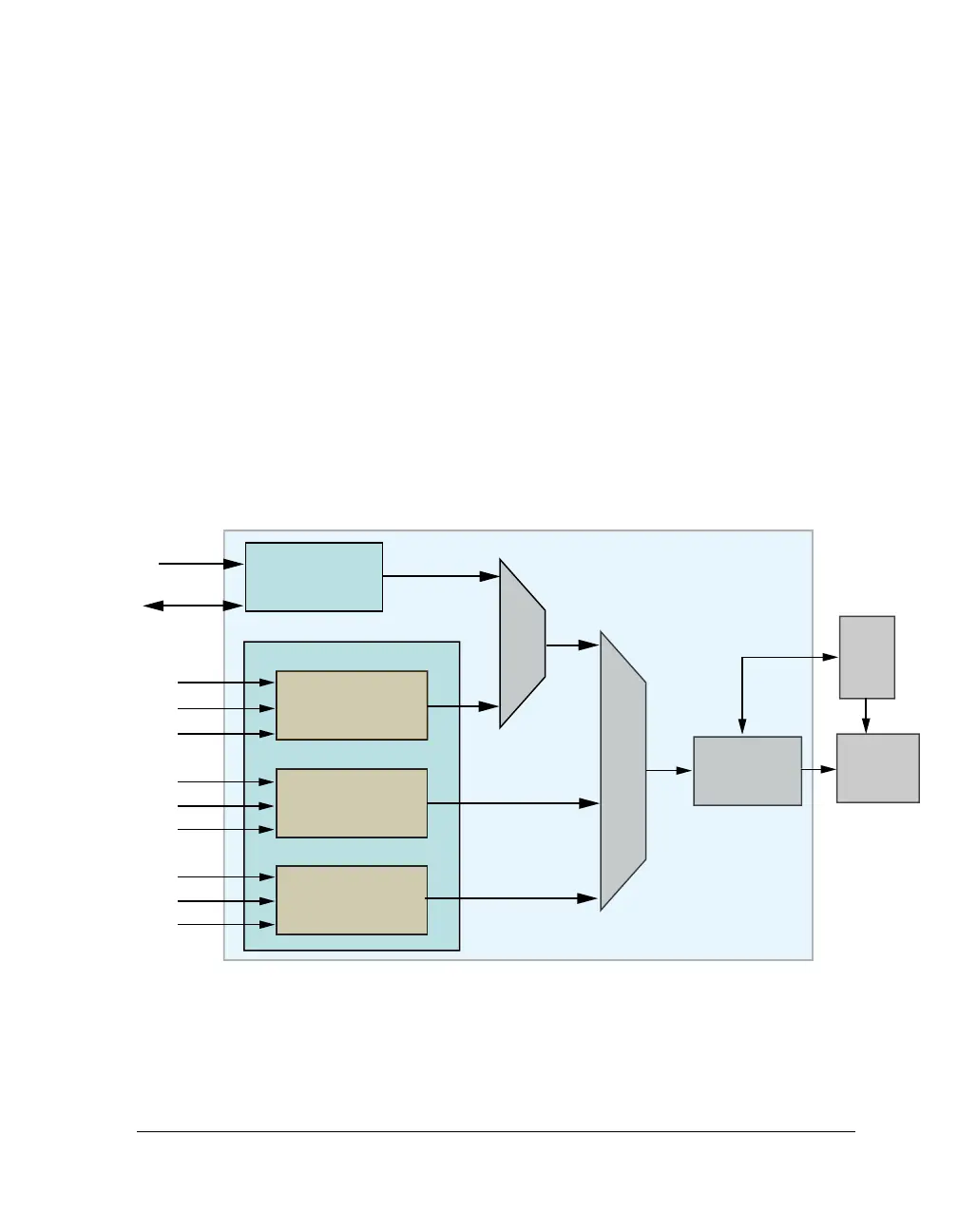

Figure 11-1 provides a graphical overview of the input data port architec-

ture. Notice that each channel is independent and contains a separate

clock and frame sync input.

The IDP provides an easy way to pump serial data into on-chip

memory since it is less complex than the traditional SPORT mod-

ule, limited to unidirectional slave transfers only.

Figure 11-1. Input Data Port

IDP_CLK_0

PDAP

Serial Input Port

IDP_FS_0

IDP_DAT_0

IDP

IDP_CLK_x

IDP_FS_x

IDP_DAT_x

IDP_CLK_7

IDP_FS_7

IDP_DAT_7

20-BIT

DATA

CONTROL

SIPx (x = 6 - 1)

SERIAL TO PARALLEL

32-BIT CONVERSION

SIP7

SERIAL TO PARALLEL

32-BIT CONVERSION

CORE

INTERNAL

MEMORY

IDP_FIFO

8 x 32-BIT

SIP0

SERIAL TO PARALLEL

32-BIT CONVERSION

CHANNEL 0

CHANNEL x

CHANNEL 7

IDP INPUT CHANNEL ARBITER

DMA

Loading...

Loading...