ADSP-214xx SHARC Processor Hardware Reference 13-5

Sony/Philips Digital Interface

clock, frame sync, data, and

EXT_SYNC (if external synchronization is

required) inputs also need to be routed through SRU (see Table 13-4).

The SRU (signal routing unit) needs to be programmed in order to con-

nect the S/PDIF receiver to the output pins or any other peripherals and

also for the connection to the input biphase stream.

Program the corresponding SRU registers to connect the outputs to the

required destinations (Table 13-5). The biphase encoded data and the

external PLL clock inputs to the receiver are routed through the signal

routing unit (SRU). The extracted clock, frame sync, and data are also

routed through the SRU.

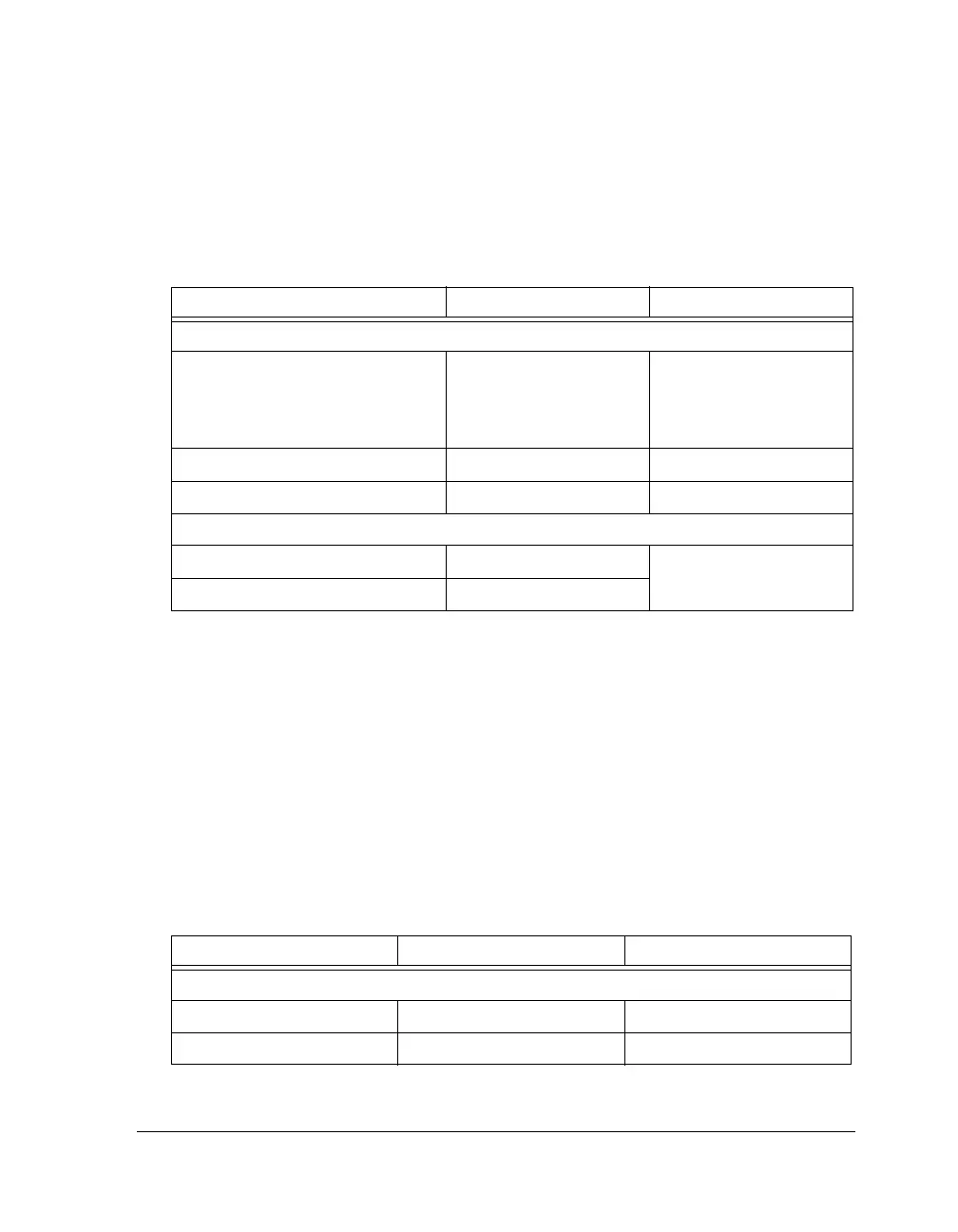

Table 13-4. S/PDIF DAI/SRU Transmitter Signal Connections

Internal Node DAI Group SRU Register

Inputs

DIT_CLK_I Group A SRU_CLK4–2

DIT_HFCLK_I

DIT_EXTSYNC_I

DIT_DAT_I Group B SRU_DAT4

DIT_FS_I Group C SRU_FS2

Outputs

DIT_O Group B, D

DIT_BLKSTART_O Group D, E

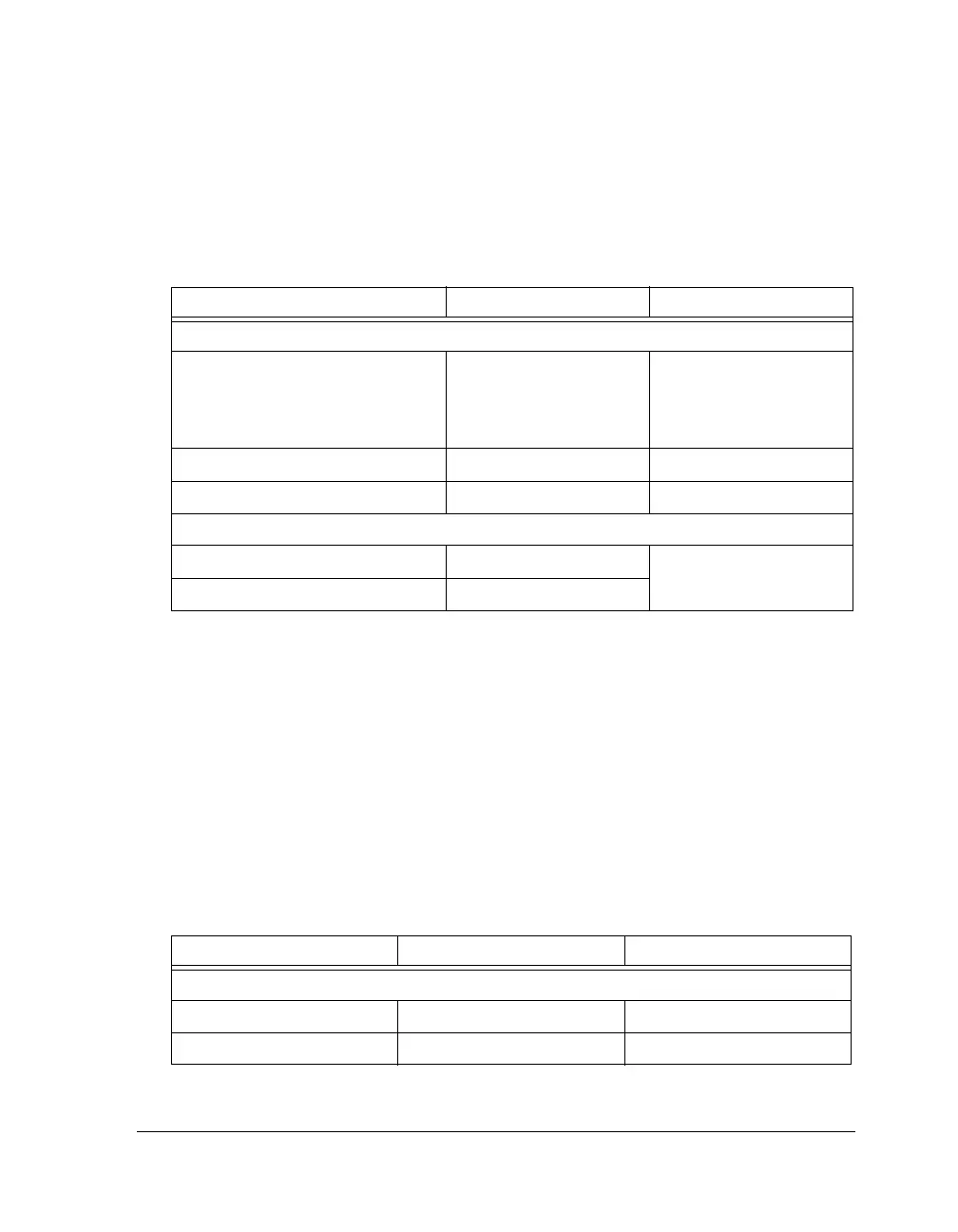

Table 13-5. S/PDIF DAI/SRU Receiver Signal Connections

Internal Node DAI Group SRU Register

Inputs

SPDIF_EXTPLLCLK_I Group A SRU_CLK4

DIR_I Group C SRU_DAT5

Loading...

Loading...