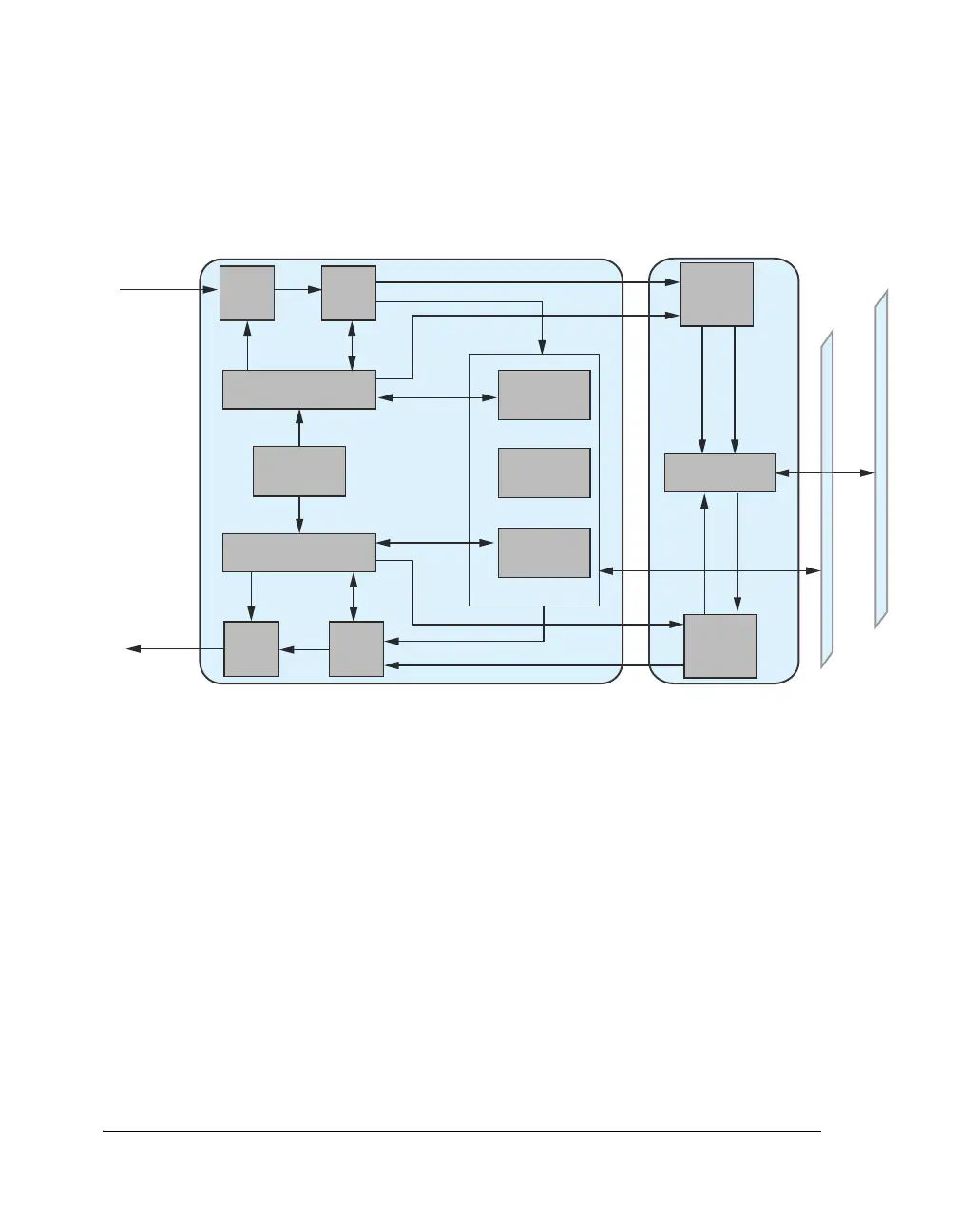

Functional Description

20-6 ADSP-214xx SHARC Processor Hardware Reference

the RS-485 data interface standard. The UART has its own set of control

and status registers (Figure 20-1).

The UART is a DMA-capable peripheral with support for separate trans-

mit and receive DMA master channels. It can be used in either DMA or

core modes of operation. The core mode requires software management of

the data flow using either interrupts or polling. The DMA method

requires minimal software intervention as the DMA engine itself moves

the data. For more information, see “DMA Transfers” on page 20-13.

Either one of the peripheral timers can be used to provide a hard-

ware-assisted autobaud detection mechanism for use with the UART. See

the “Autobaud Detection” on page 20-21.

Figure 20-1. UART Functional Block Diagram

RX

SR

BAUD

GENERATOR

MASTER

RX

DMA

MASTER

TX

DMA

CORE

BUS

IOD0

BUS

UARTx_RX_I

UARTx_TX_O

RX

RBR

RX CONTROL

TX CONTROL

TX

SR

TX

RBR

LINE CONTROL/

STATUS

DIVISOR

LATCH

LINE CONTROL/

STATUS

CORE INTERFACE

UART DMA

ARBITER/DATA MUX

Loading...

Loading...