ADSP-214xx SHARC Processor Hardware Reference 21-7

Two Wire Interface Controller

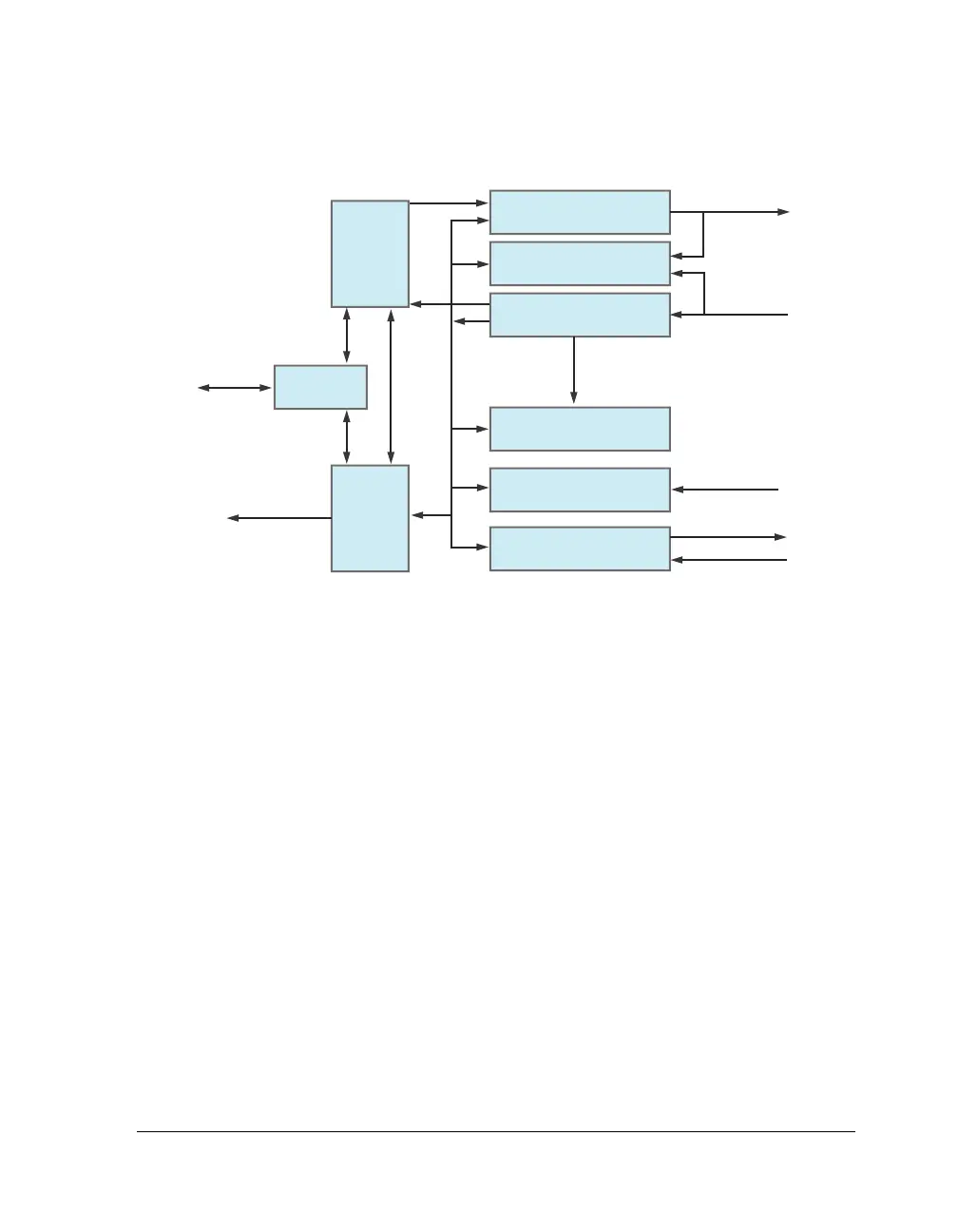

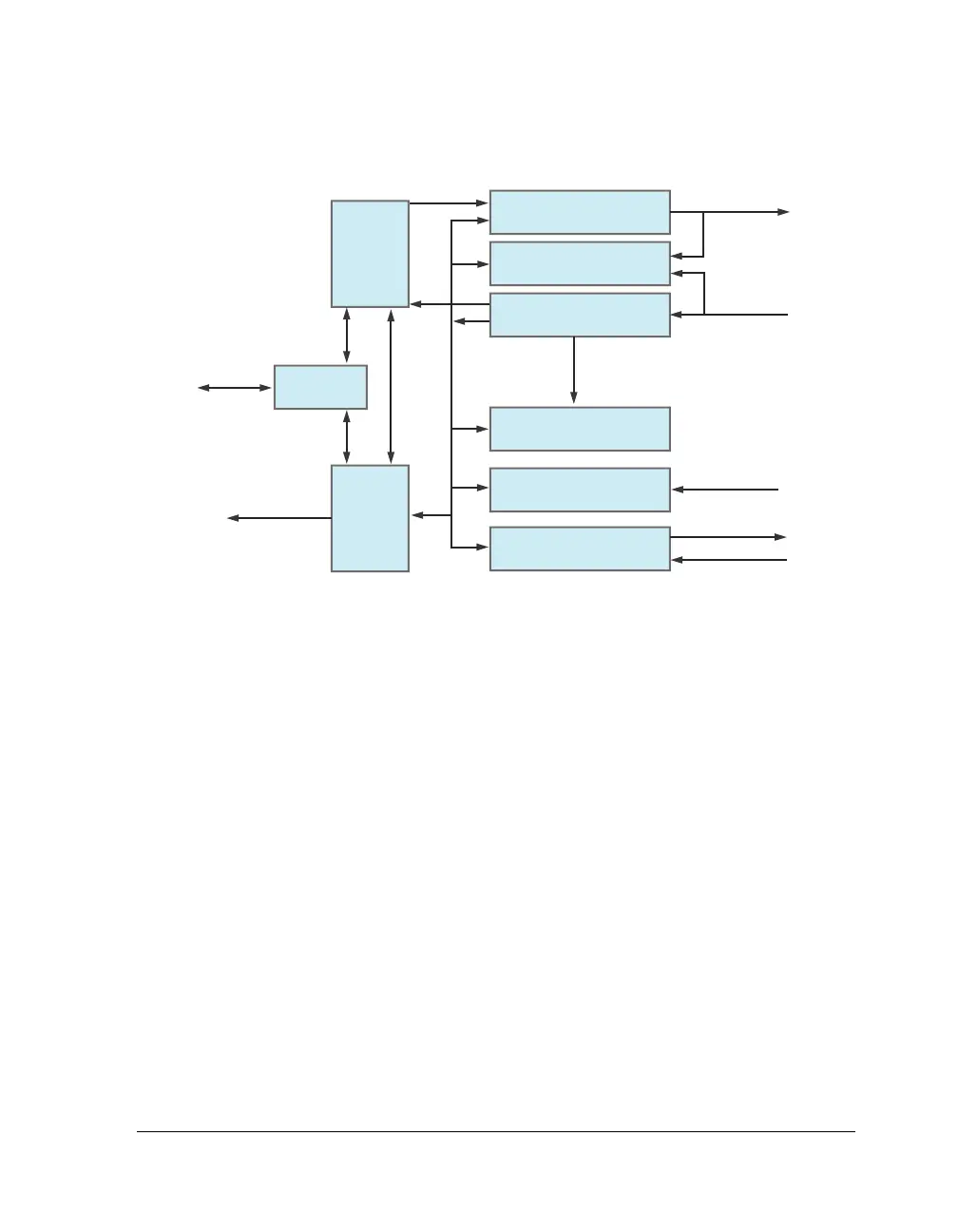

The address compare block supports address comparison in the event the

TWI controller module is accessed as a slave.

The prescaler block must be programmed to generate a 10 MHz time ref-

erence relative to the peripheral clock. This time base is used for filtering

data and timing events specified by the electrical parameters in the data

sheet (see the I

2

C bus specification from Philips), as well as for TWI_CLOCK

clock generation.

The clock generation module is used to generate an external serial clock

(

TWI_CLOCK) when in master mode. It includes the logic necessary for syn-

chronization in a multimaster clock configuration and clock stretching

when configured in slave mode.

Figure 21-1. TWI Block Diagram

IRQ

TWI_DATA_I

(OPEN DRAIN)

REGISTERS

TWI

INTERFACE

CLOCK GENERATION

PRESCALER

ADDRESS COMPARE

RECEIVE SHIFT

REGISTER

ARBITRATION

TRANSMIT SHIFT

REGISTER

FIFO

TWI_DATA_PBEN_O

(OPEN DRAIN)

CORE BUS

PCLK

TWI_CLK_PBEN_O

TWI_CLK_I

Loading...

Loading...