Functional Description

21-8 ADSP-214xx SHARC Processor Hardware Reference

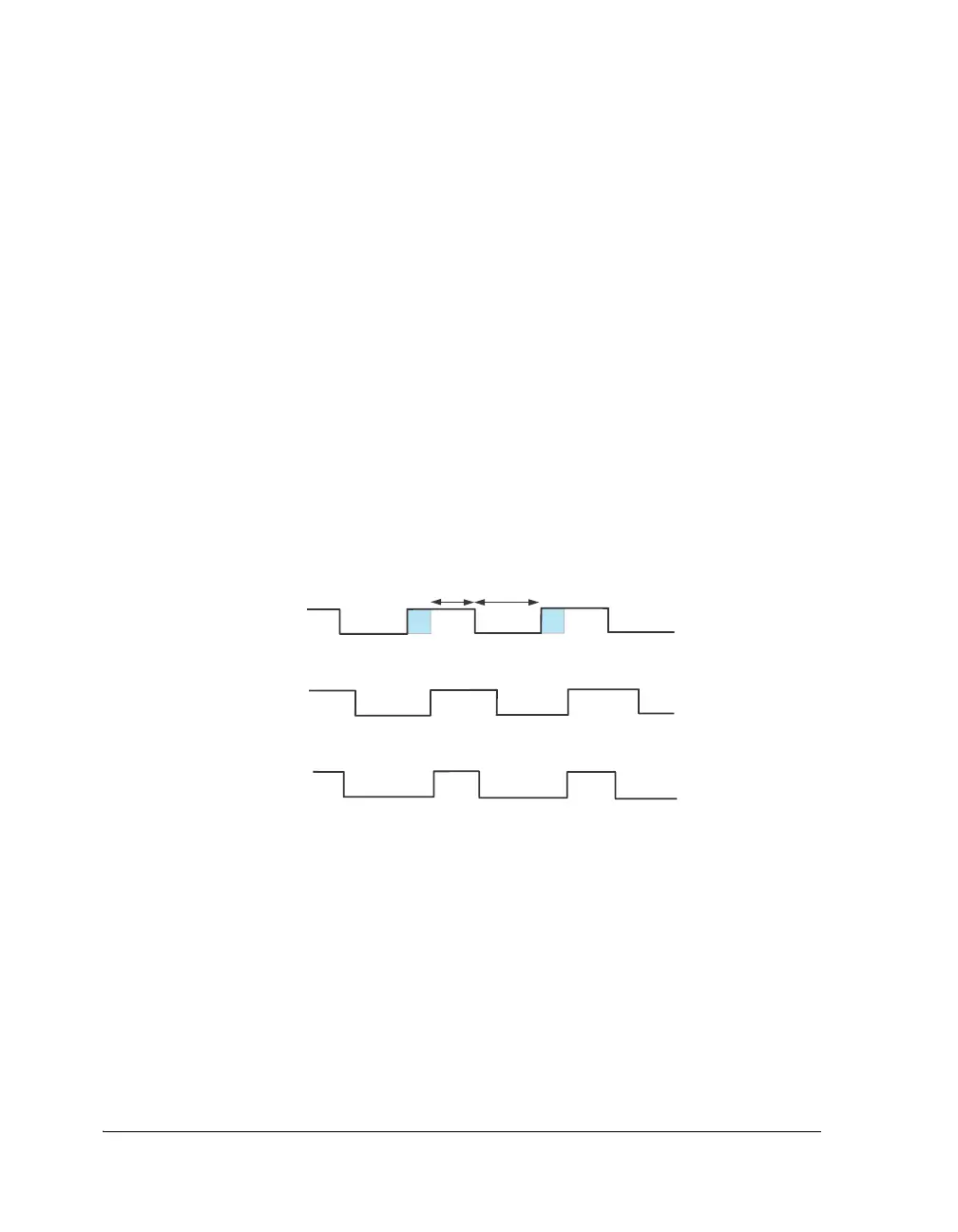

The TWI controller’s clock output follows these rules:

• Once the clock high (

CLKHI) count is complete, the serial clock out-

put is driven low and the clock low (CLKLOW) count begins.

• Once the clock low count is complete, the serial clock line is

three-stated and the clock synchronization logic enters into a delay

mode (shaded area) until the TWI_CLOCK line is detected at a logic 1

level. At this time, the clock high count begins.

The TWI controller only issues a clock during master mode operation and

only at the time a transfer has been initiated. If arbitration for the bus is

lost, the serial clock output immediately three-states. If multiple clocks

attempt to drive the serial clock line, the TWI controller synchronizes its

clock with the other remaining clocks. This is illustrated in Figure 21-2.

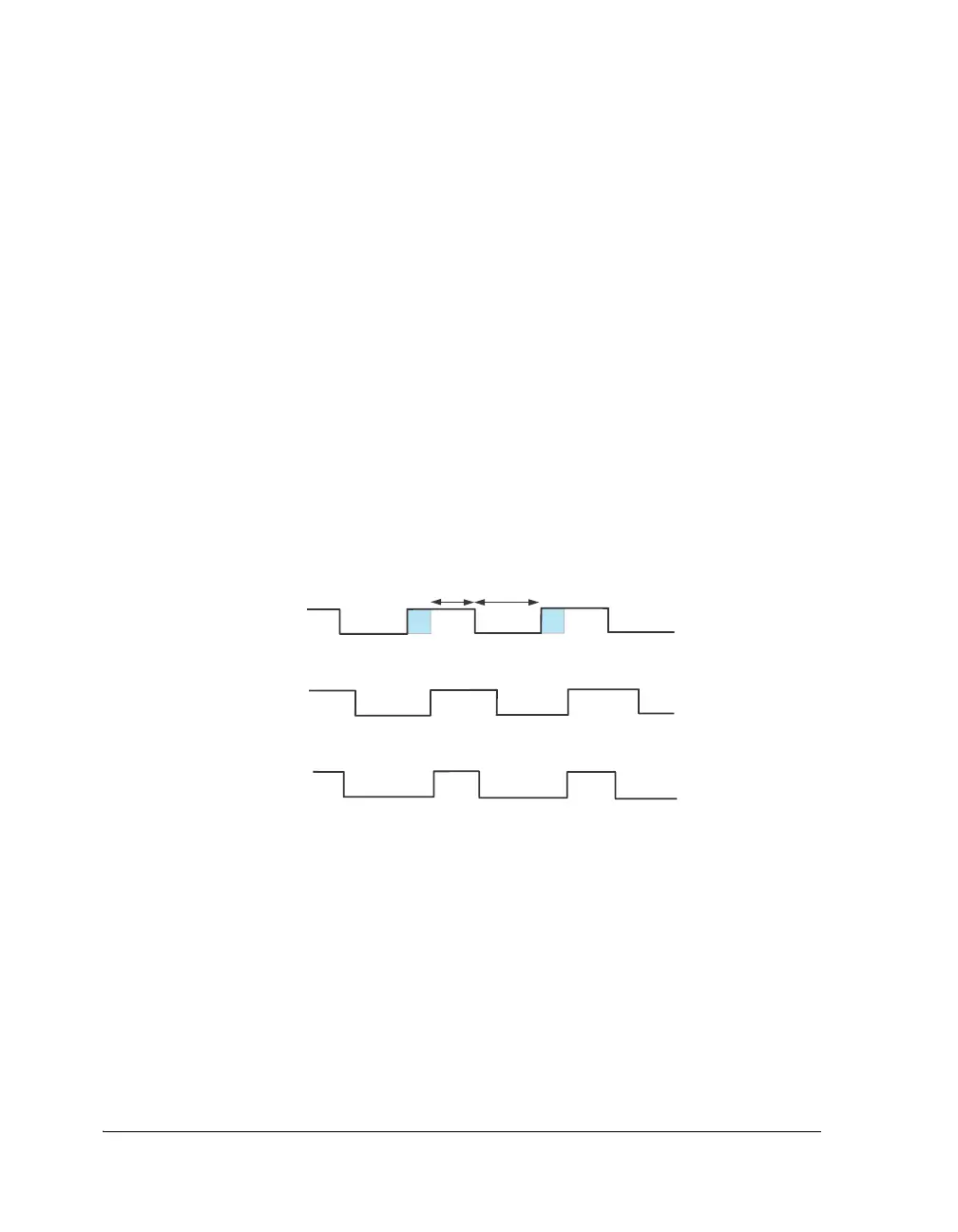

The TWI controller follows the transfer protocol of the Philips I

2

C Bus

Specification version 2.1 dated January 2000. A simple complete transfer is

diagrammed in Figure 21-3.

Figure 21-2. TWI Clock Synchronization

HIGH

LOW

COUNT

TWI CONTROLLER

CLOCK

SECOND MASTER

CLOCK

TWI_CLOCK

RESULT

Loading...

Loading...