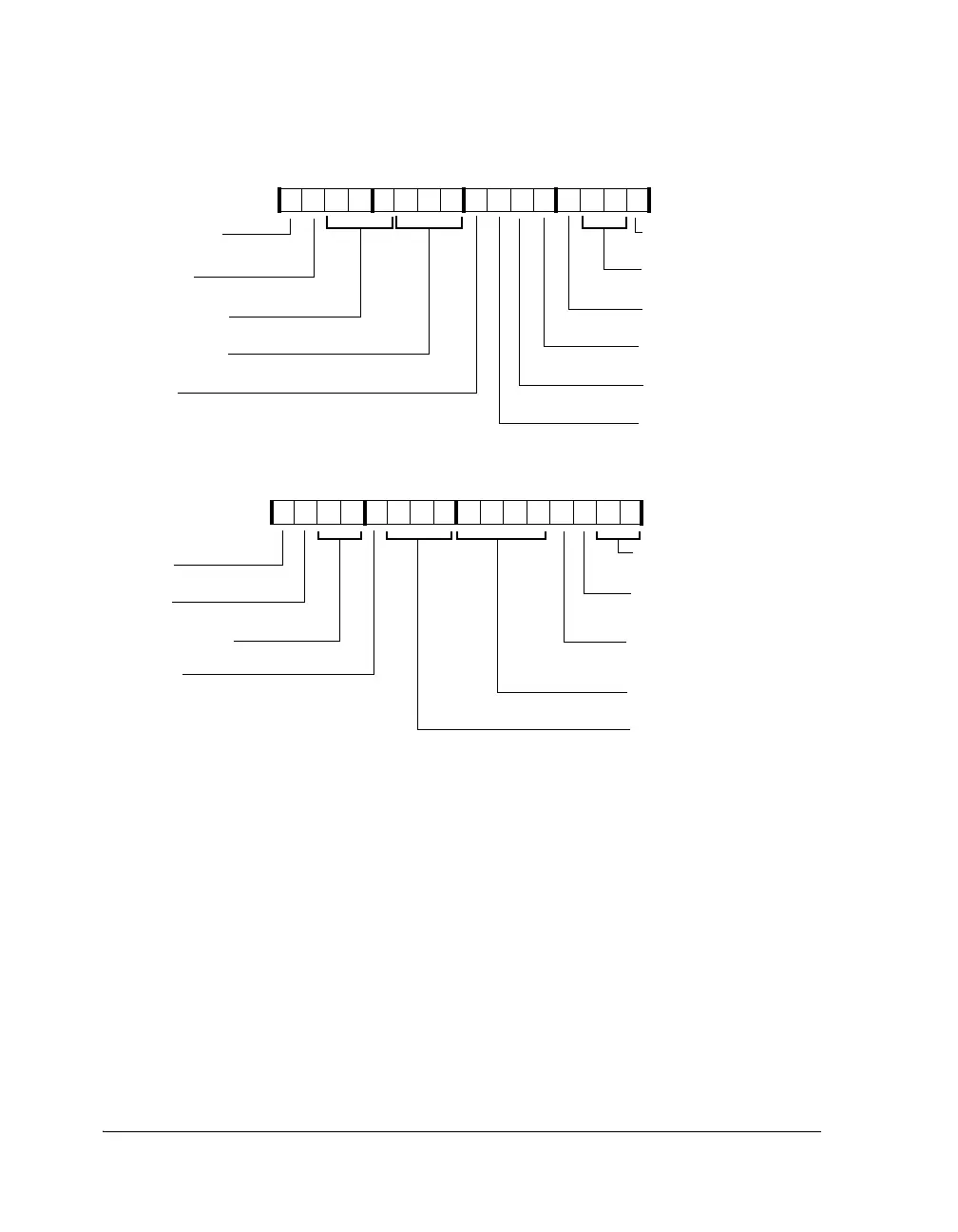

SDBUF

Row Address Width

X16DE

SDRAM External Data Path Width

SDRAW (29–27)

SDRAM tRCD Specification

SDTWR (18–17)

SDRAM tWR Specification

SDADDRMODE

SDORF

Pipeline Option with External Register Buffer

FAR

Optional Refresh

Force Auto Refresh

FPC

Force Precharge

STDRCD (26–24)

Force LMR

Address Map Mode

PGSZ 128

Page size is 128 bits

Force Auto Load Mode

Register

SDCL (2–0)

SDSRF

SDRAM Self Refresh Enable

SDPSS

SDRAM Power-up Sequence Start

DSDCTL

Disable SDCLK and Control

Signals

CAS Latency

SDPM

SDRAM Power-Up Mode

SDCAW (13–12)

SDRAM Bank Column Address Width

SDTRAS (7–4)

SDRAM tRAS Specification

SDTRP (10–8)

SDRAM tRP Specification

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

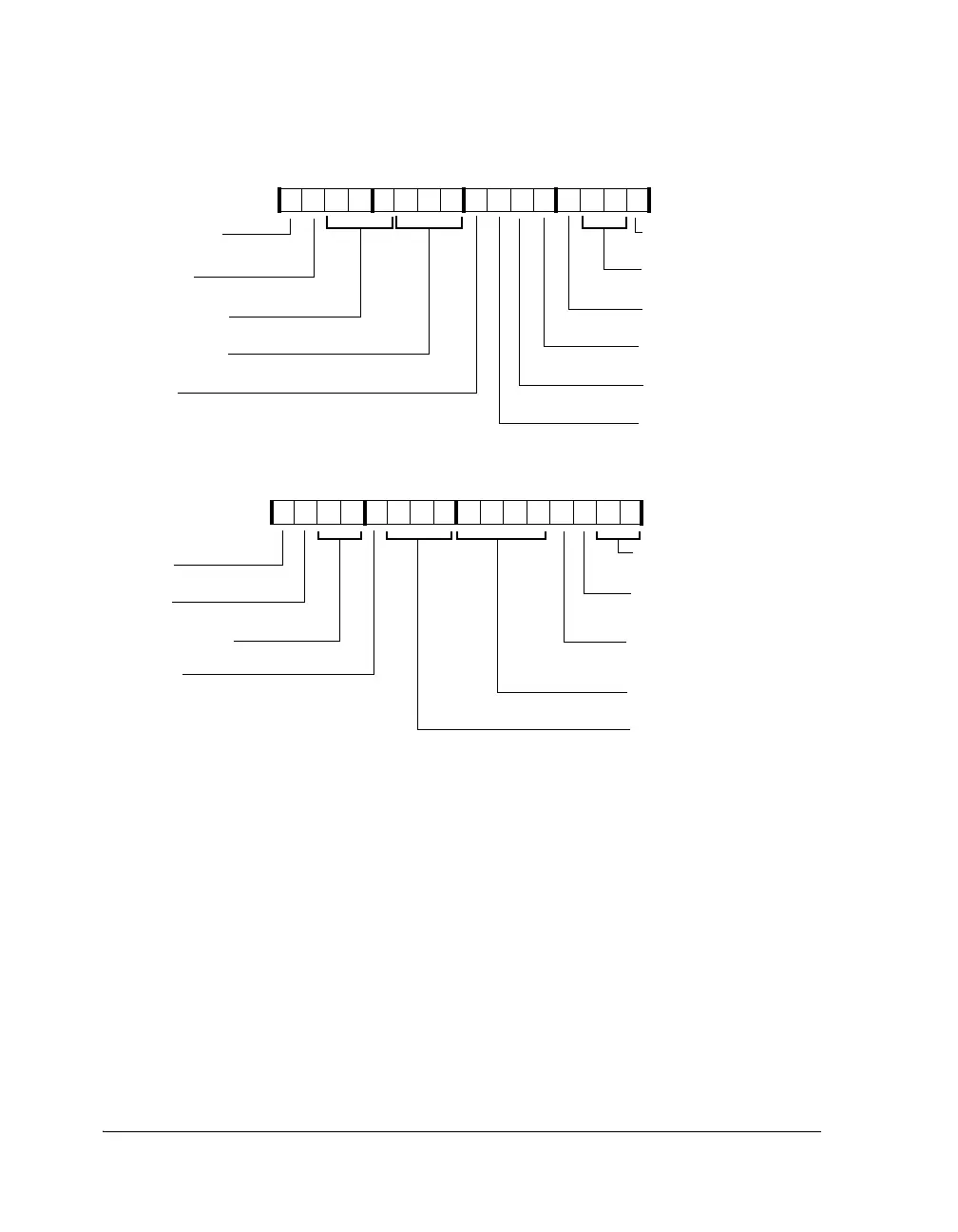

DSDCTL1

Disable SDCLK1 and Control

Signals

Loading...

Loading...