ADSP-214xx SHARC Processor Hardware Reference A-53

Registers Reference

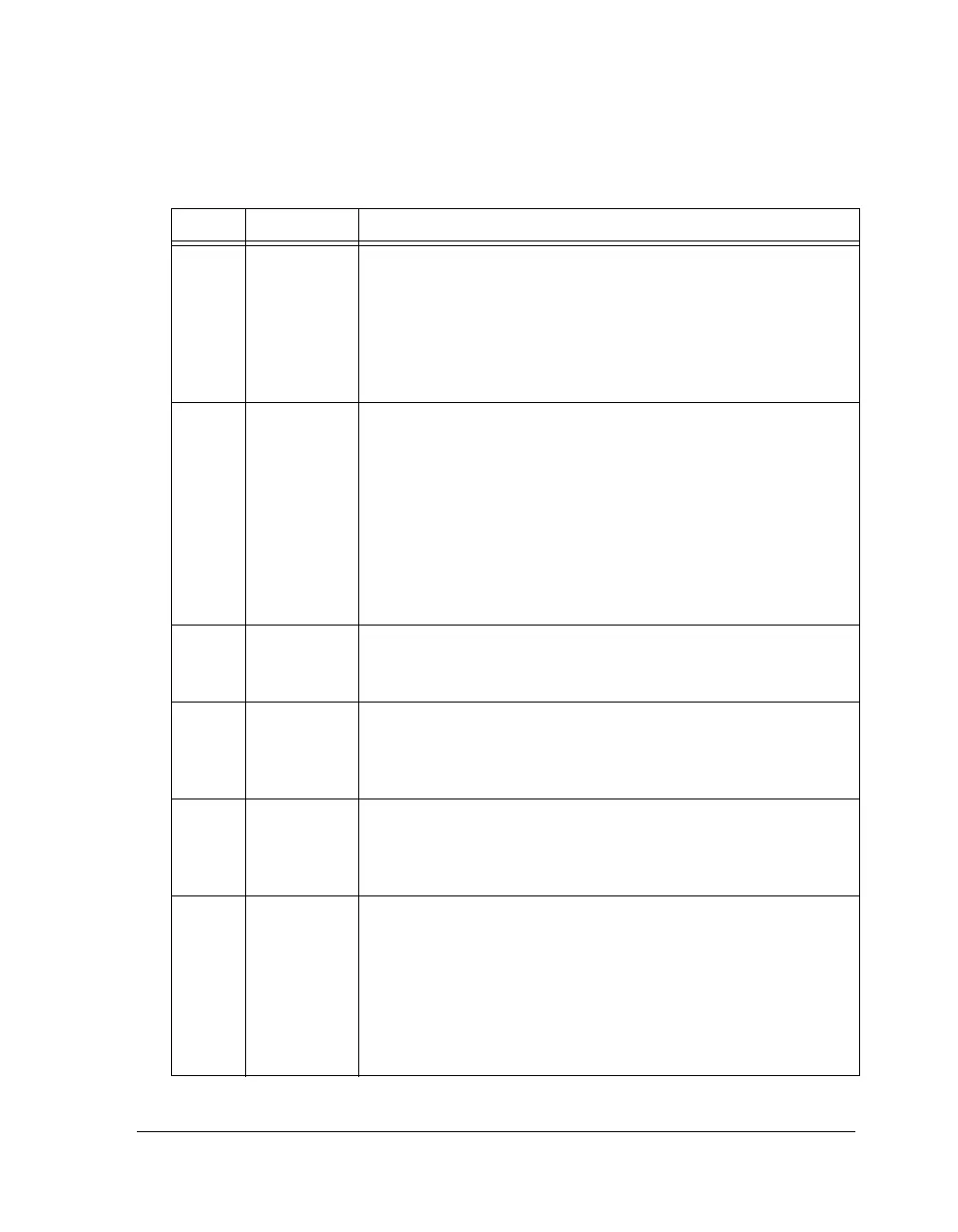

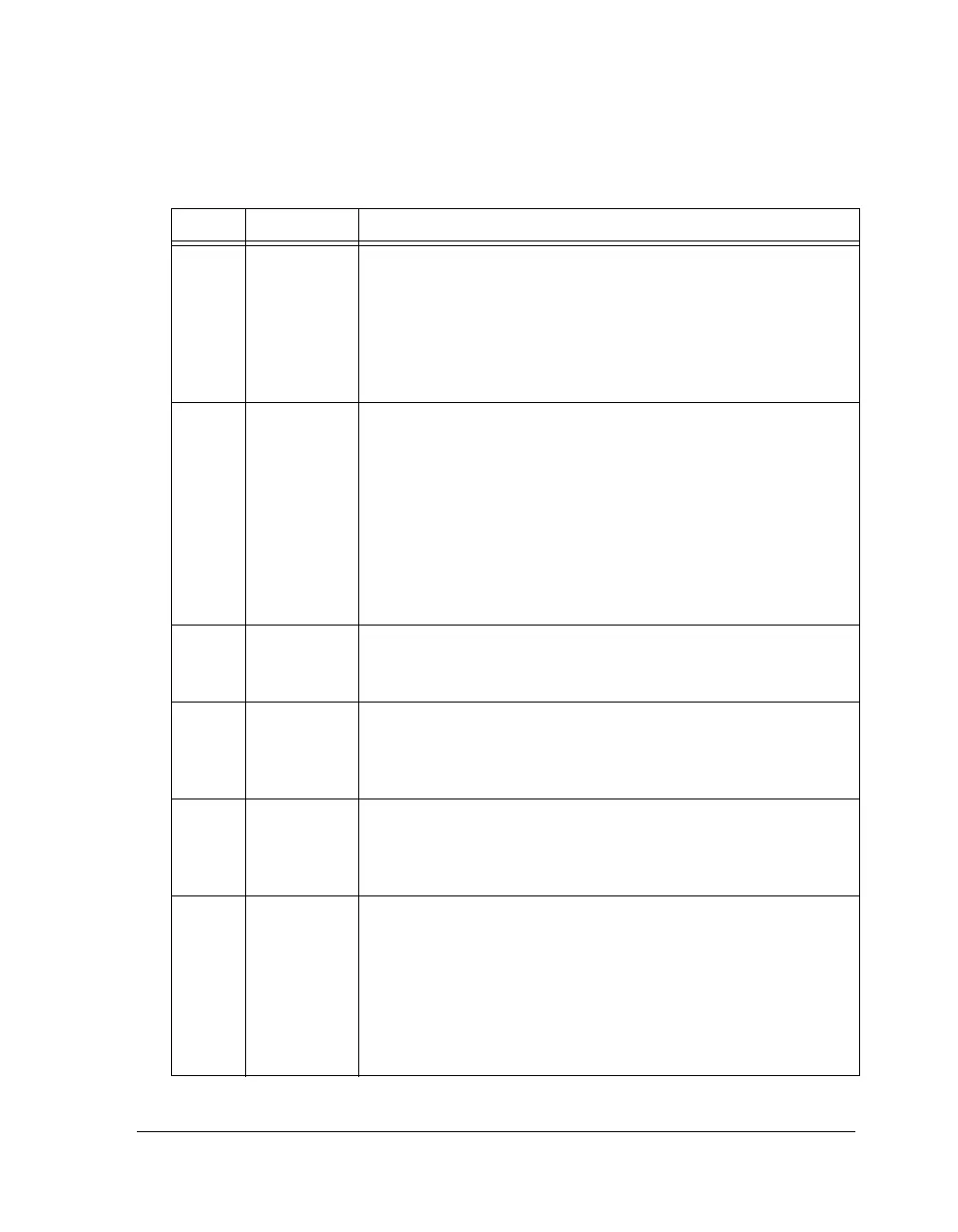

Table A-28. SDCTL Register Bit Descriptions (RW)

Bit Name Description

1–0 SDCL SDRAM CAS Latency. 2–3 SDCLK cycles. The delay in clock cycles

between when the SDRAM detects the read command and when it

provides the data at its output pins.

00, 01 = Reserved

10 = 2 cycles

11 = 3 cycles

A CAS latency of 2 is supported only up to 133 MHz SDCLK.

2DSDCTLDisable Controller and Clocks. Used to enable or disable the SDC. If

DSDCTL is disabled, any access to SDRAM address space does not

occur externally. When DSDCTL is disabled, all SDC control pins

are in their inactive states and the SDRAM clock SDCLK is not run-

ning.

1 = Disable

0 = Activate

When not using SDRAM or when using parts without an external

port, systems should disable this bit as early as possible after booting

to reduce power consumption.

3DSDCLK1Disable Clock SDCLK1. For ADSP-2148x only.

1 = No effect

0 = Disable SDCLK1

7–4 SDTRAS tRAS Specification. Row Active Open Delay is 1–15 SDCLK cycles.

Based on the system clock frequency and the timing specifications of

the SDRAM used. Programmed parameters apply to all four banks in

the external memory. Refer to the SDRAM data sheet.

10–8 SDTRP tRP Specification. Row Precharge Delay is 1–8 SDCLK cycles. Based

on the system clock frequency and the timing specifications of the

SDRAM used. Programmed parameters apply to all four banks in the

external memory. Refer to the SDRAM datas heet.

11 SDPM SDRAM Power-Up Mode. The SDPM and SDPSS bits work

together to specify and trigger an SDRAM power-up (initialization)

sequence. If the SDPM bit is set (=1), the SDC does a precharge all

command, followed by a load mode register command, followed by

eight auto-refresh cycles. If the SDPM bit is cleared (=0), the SDC

does a precharge all command, followed by eight auto-refresh cycles,

followed by a load mode register command.

Refer to the SDRAM data sheet.

Loading...

Loading...