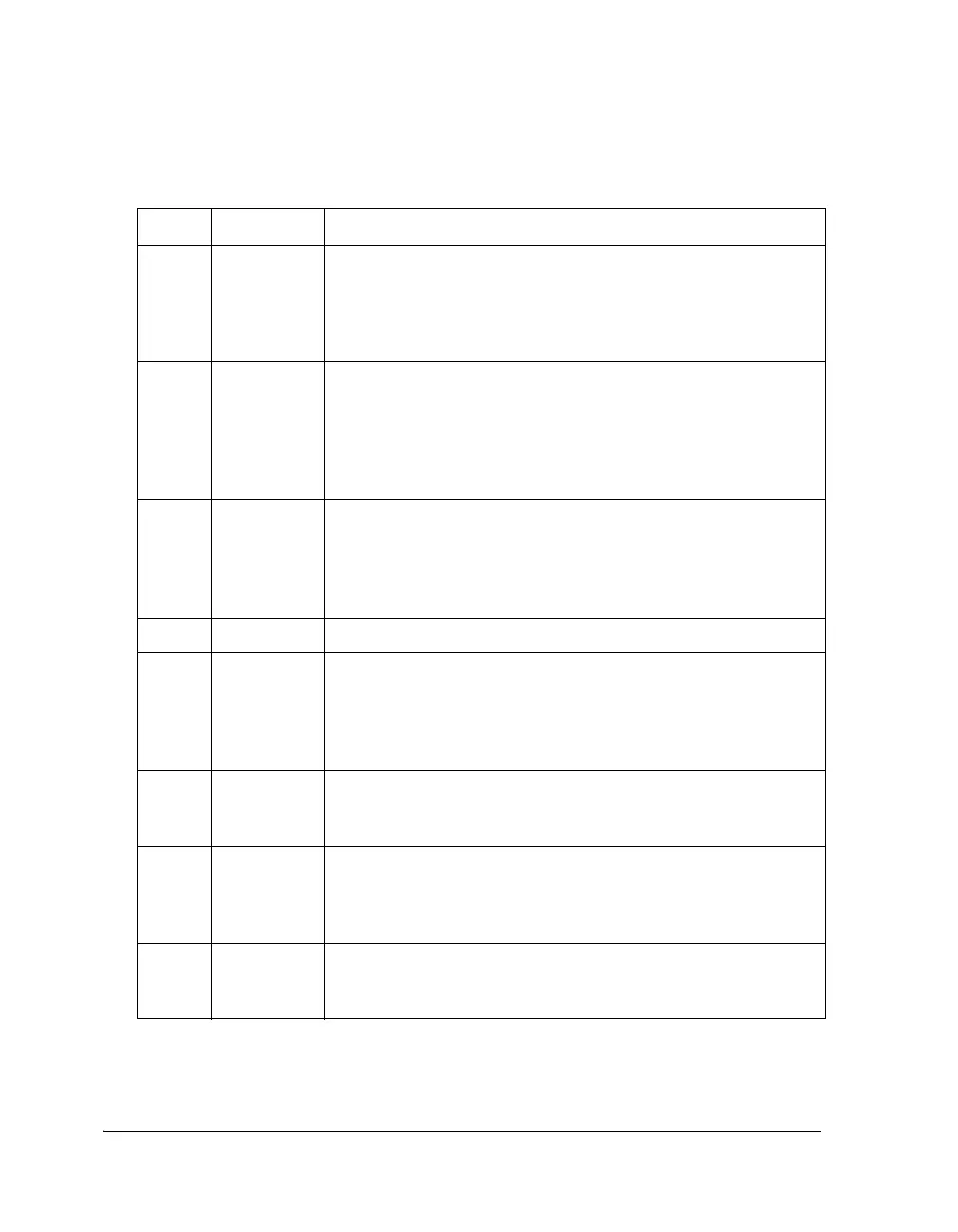

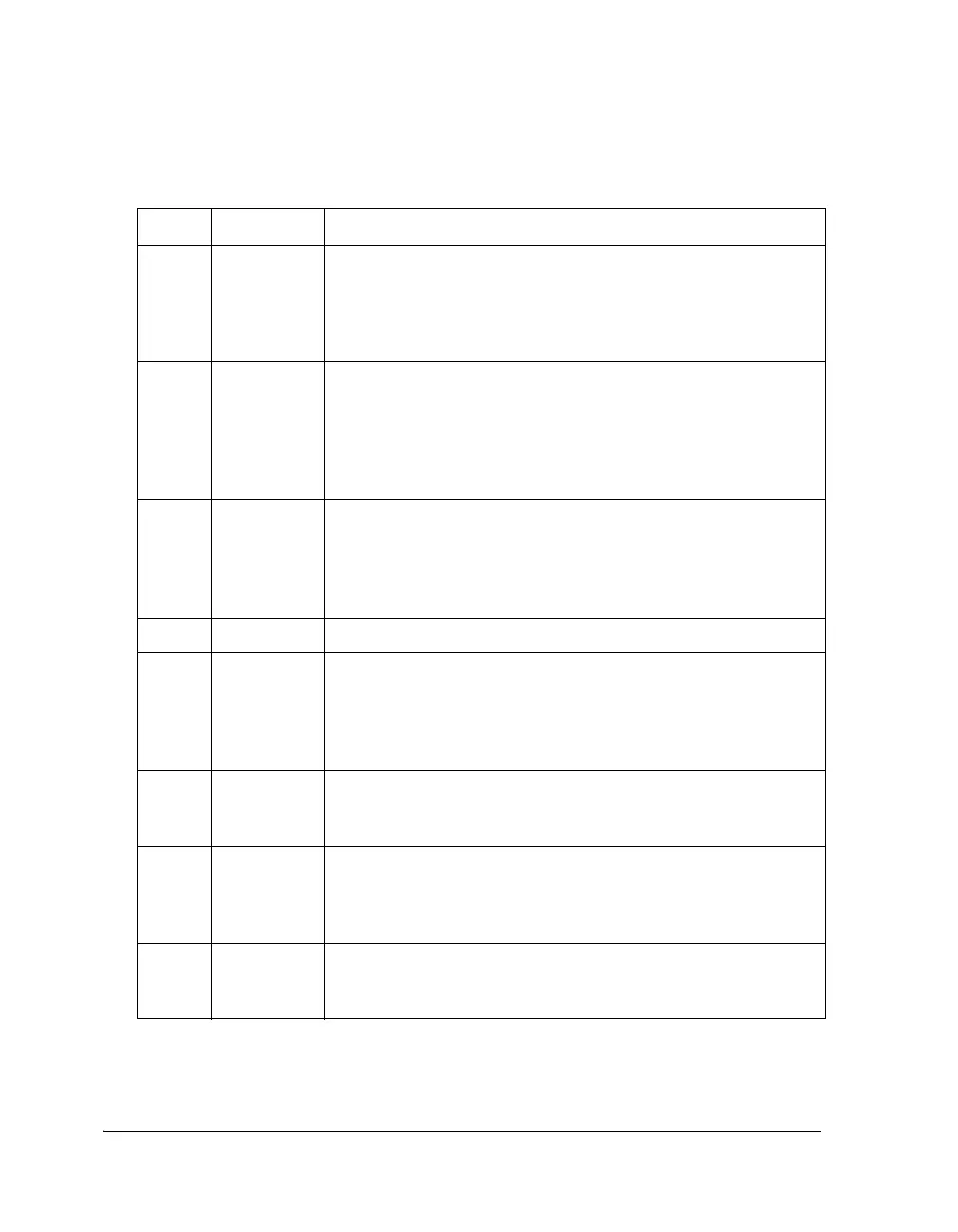

ADSP-2147x, ADSP-2148x External Port Registers

A-54 ADSP-214xx SHARC Processor Hardware Reference

13–12 SDCAW SDRAM Bank Column Address Width. SDRAM Page Size.

00 = 8 bits

01 = 9 bits

10 = 10 bits

11 = 11 bits

14

(WO)

SDPSS SDRAM Power-Up Sequence Start. The power-up sequence is trig-

gered by setting this bit. Note that there is a latency for this first

access to SDRAM because the SDRAM power-up sequence takes

many cycles to complete.

0 = No effect

1 = Enable power-up on next SDRAM access

15

(WO)

SDSRF Self-Refresh Enable. When the SDSRF bit is set to 1, self-refresh

entry command is triggered. Once the SDC completes any active

transfers, the SDC executes the sequence of commands to put the

SDRAM into self-refresh mode. Any access to the enabled SDRAM

bank causes the SDC to trigger a self-refresh exit command.

16 X16DE SDRAM External Data Path Width. This bit should always be set.

18–17 SDTWR tWR Specification. Write To Precharge Delay) is 1–3 SDCLK cycles.

Based on the system clock frequency and the timing specifications of

the SDRAM used. Programmed parameters apply to all four banks in

the external memory.

Refer to the SDRAM data sheet.

19 SDORF Optional Auto-Refresh Command.

0 = Auto-refresh occurs when refresh counter expires

1 = Auto-refresh not performed

20

(WO)

FAR Force Auto-Refresh Command. Performs an auto-refresh immedi-

ately.

0 = No effect

1 = Force auto-refresh

21

(WO)

FPC Force Precharge. Performs a precharge all immediately.

0 = No effect

1 = Force precharge

Table A-28. SDCTL Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...