DAI Signal Routing Unit Registers

A-122 ADSP-214xx SHARC Processor Hardware Reference

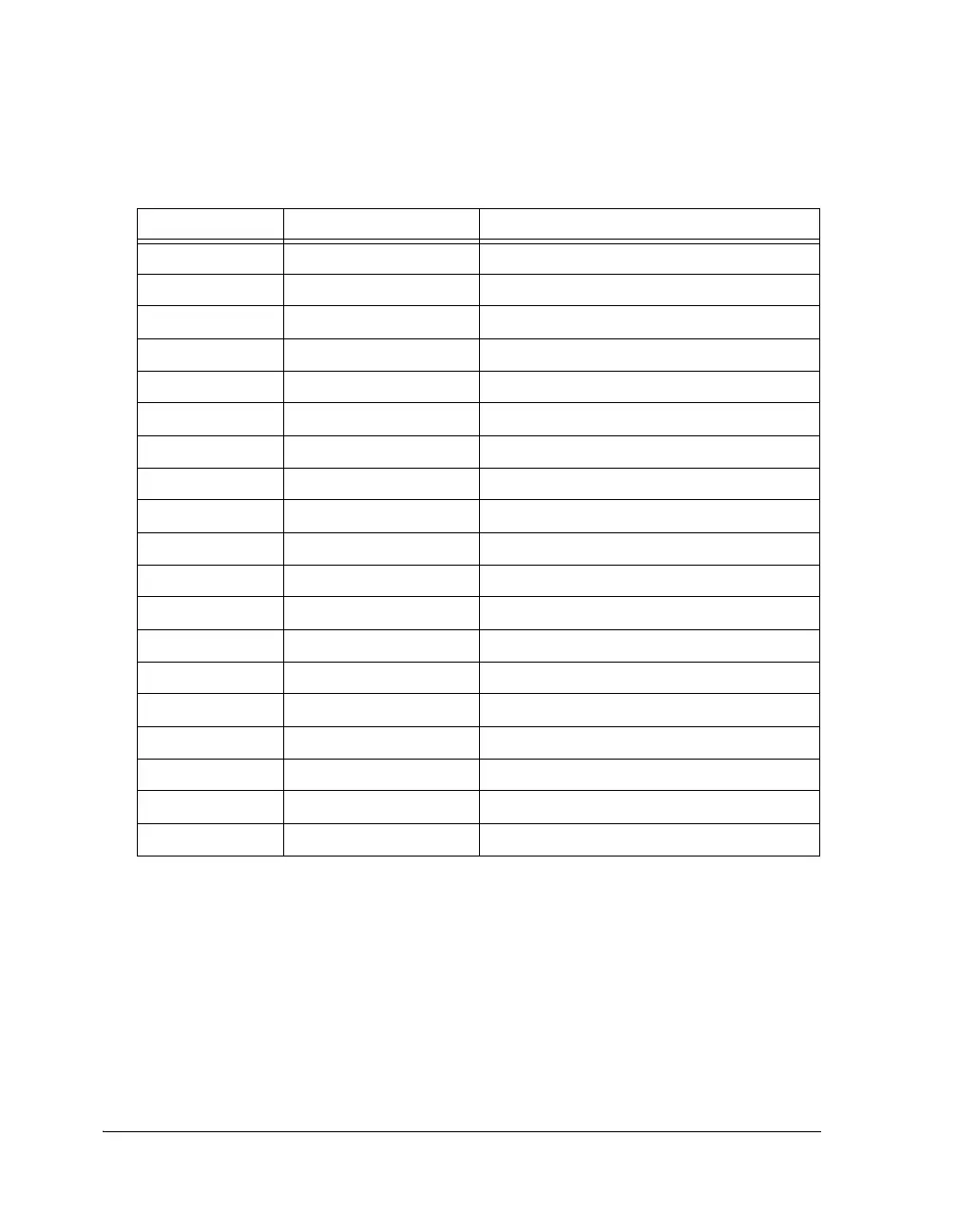

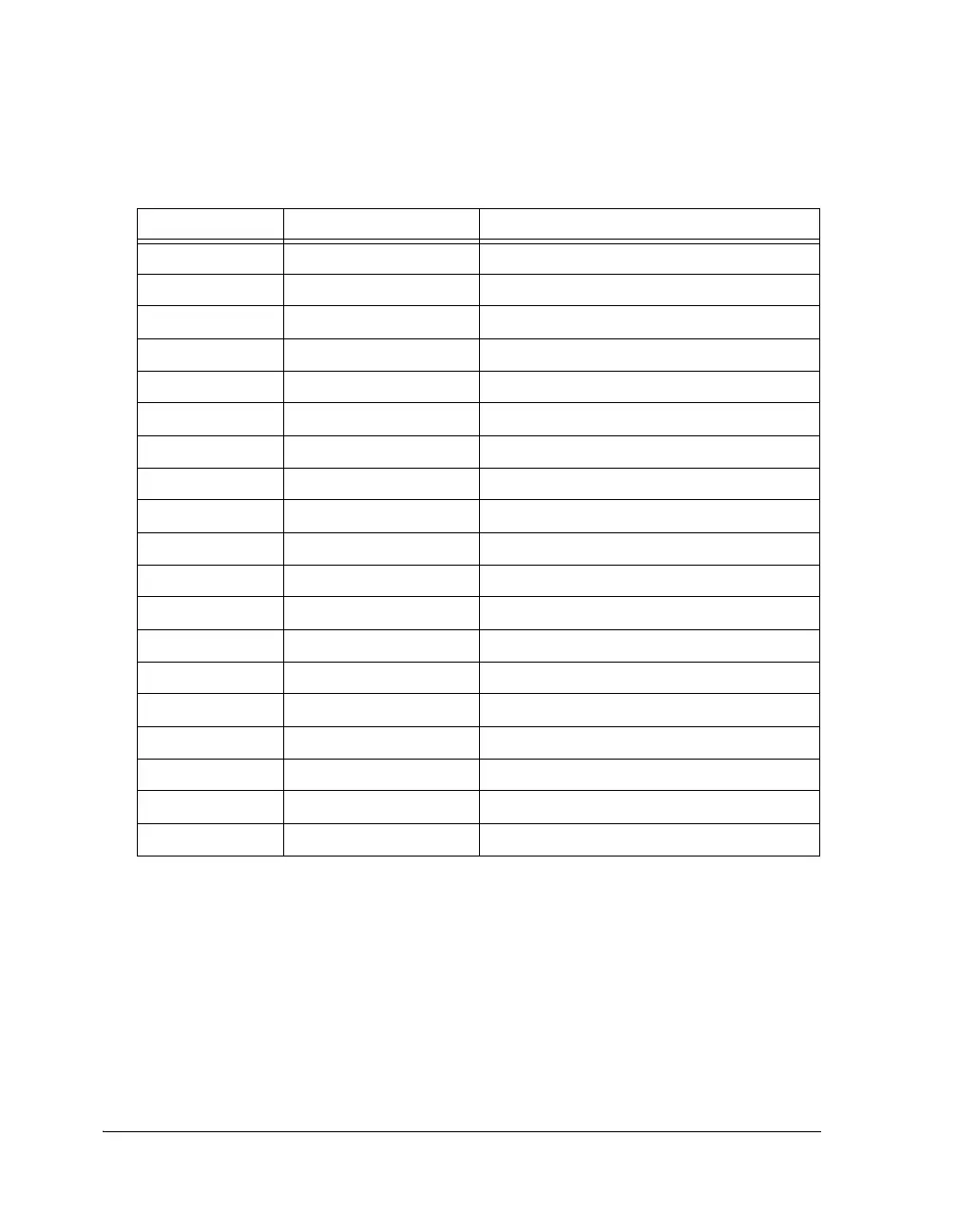

01101 (0xD) DAI_PB14_O Pin Buffer 14

01110 (0xE) DAI_PB15_O Pin Buffer 15

01111 (0xF) DAI_PB16_O Pin Buffer 16

10000 (0x10) DAI_PB17_O Pin Buffer 17

10001 (0x11) DAI_PB18_O Pin Buffer 18

10010 (0x12) DAI_PB19_O Pin Buffer 19

10011 (0x13) DAI_PB20_O Pin Buffer 20

10100 (0x14) SPORT0_CLK_O SPORT 0 Clock

10101 (0x15) SPORT1_CLK_O SPORT 1 Clock

10110 (0x16) SPORT2_CLK_O SPORT 2 Clock

10111 (0x17) SPORT3_CLK_O SPORT 3 Clock

11000 (0x18) SPORT4_CLK_O SPORT 4 Clock

11001 (0x19) SPORT5_CLK_O SPORT 5 Clock

11010 (0x1A) DIR_CLK_O SPDIF Receive Clock Output

11011 (0x1B) DIR_TDMCLK_O SPDIF Receive TDM Clock Output

11100 (0x1C) PCG_CLKA_O Precision Clock A Output

11101 (0x1D) PCG_CLKB_O Precision Clock B Output

11110 (0x1E) LOW Logic Level Low (0)

11111 (0x1F) HIGH Logic Level High (1)

Table A-75. Group A Sources – Serial Clock (Cont’d)

Selection Code Source Signal Description (Source Selection)

Loading...

Loading...