DAI Signal Routing Unit Registers

A-134 ADSP-214xx SHARC Processor Hardware Reference

Setting

SRU_PIN4 bit 28 to high inverts the level of DAI_PB19_I and setting

SRU_PIN4 bit 29 to high inverts the level of DAI_PB20_I. Input Inversion

only works if the buffer output is not routed to its input.

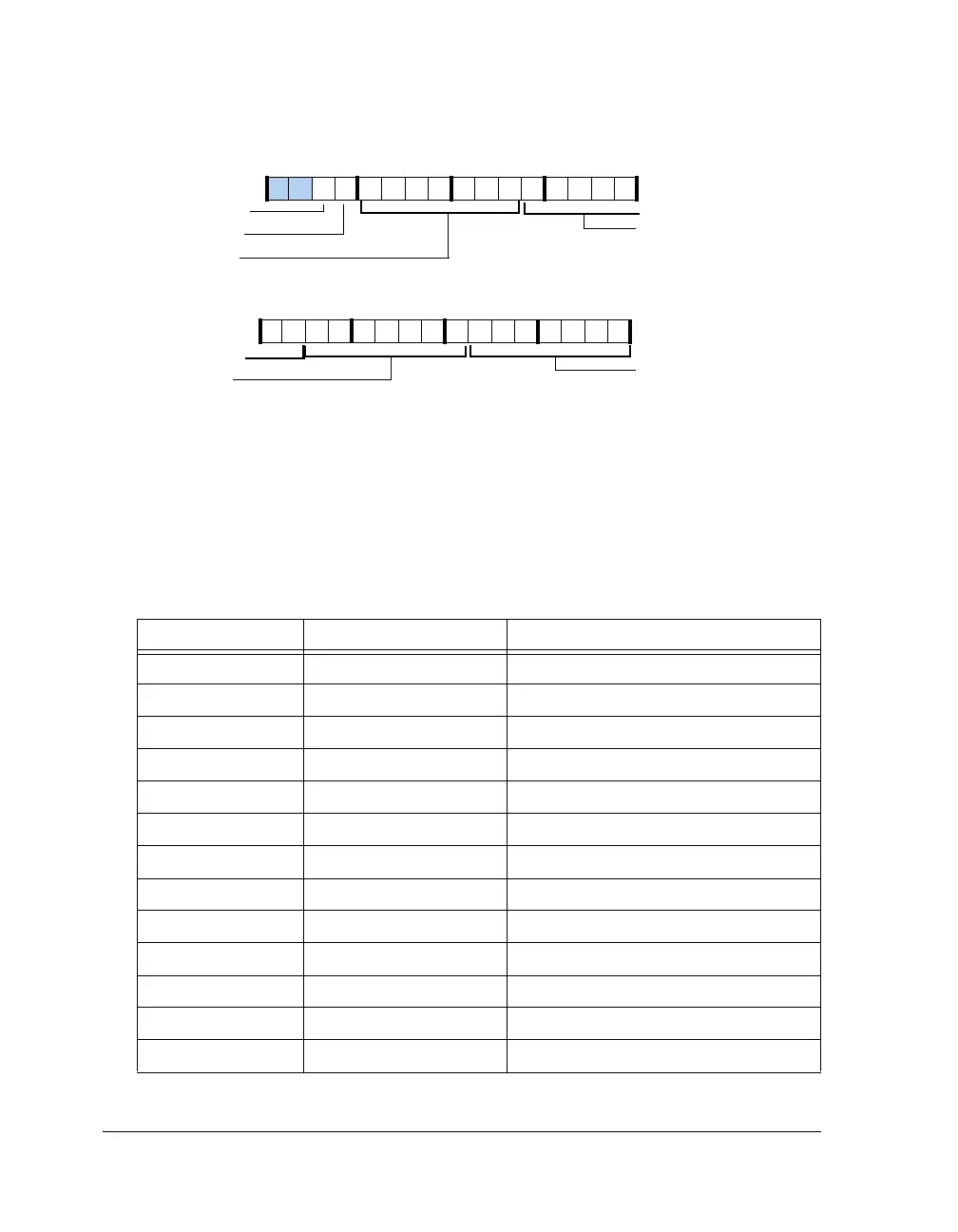

Figure A-74. SRU_PIN4 Register (RW)

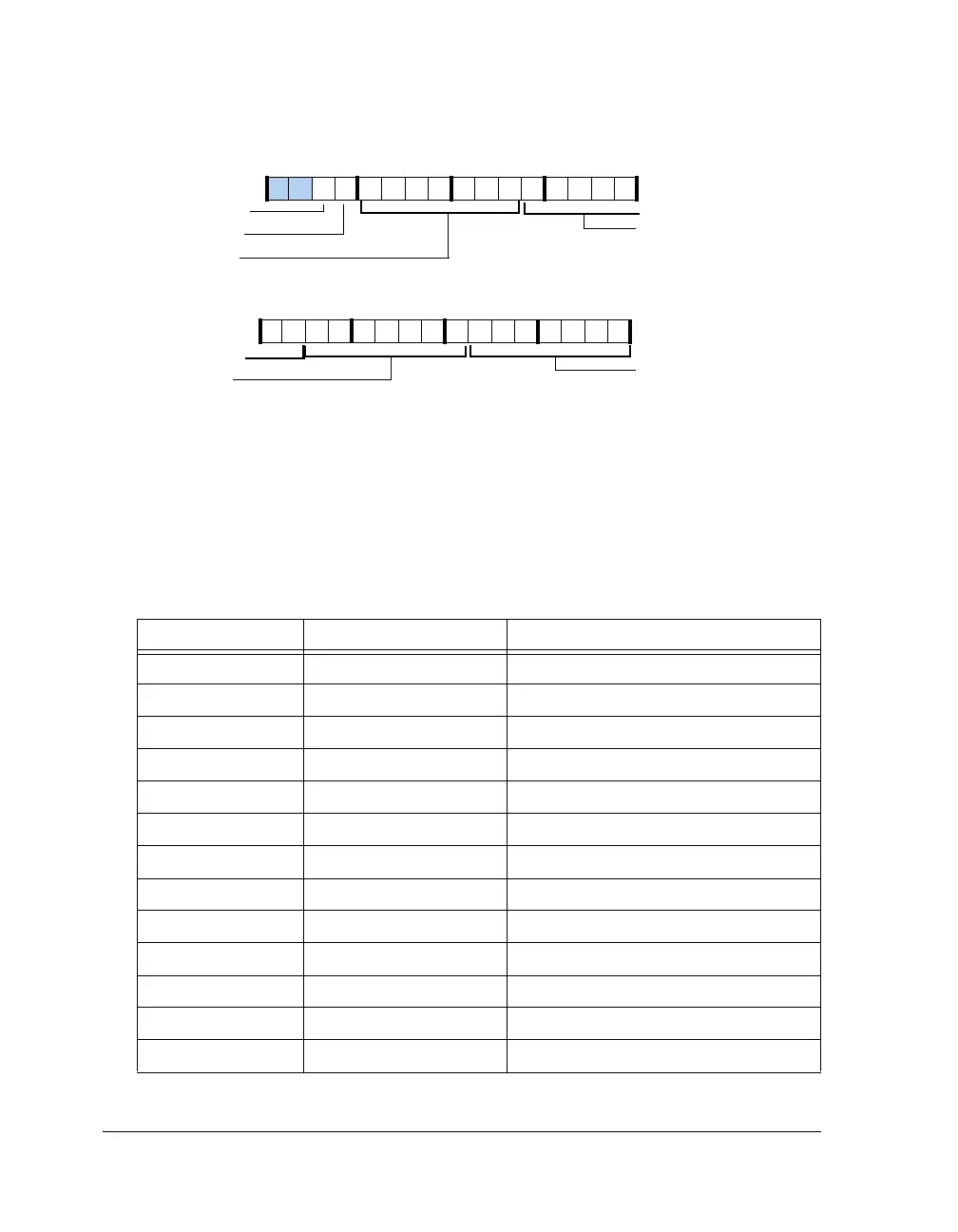

Table A-78. Group D Sources – Pin Signal Assignments

Selection Code Source Signal Description (Source Selection)

0000000 (0x0) DAI_PB01_O Pin Buffer 1

0000001 (0x1) DAI_PB02_O Pin Buffer 2

0000010 (0x2) DAI_PB03_O Pin Buffer 3

0000011 (0x3) DAI_PB04_O Pin Buffer 4

0000100 (0x4) DAI_PB05_O Pin Buffer 5

0000101 (0x5) DAI_PB06_O Pin Buffer 6

0000110 (0x6) DAI_PB07_O Pin Buffer 7

0000111 (0x7) DAI_PB08_O Pin Buffer 8

0001000 (0x8) DAI_PB09_O Pin Buffer 9

0001001 (0x9) DAI_PB10_O Pin Buffer 10

0001010 (0xA) DAI_PB11_O Pin Buffer 11

0001011 (0xB) DAI_PB12_O Pin Buffer 12

0001100 (0xC) DAI_PB13_O Pin Buffer 13

DAI_PB19_I (20–14)

DAI_PB19_I (20–14) (con’t)

DAI_PB18_I (13–7)

DAI_PB17_I (6–0)

DAI_PB20_I (27–21)

DAI Pin Buffer 19 Input

DAI Pin Buffer 17 Input

DAI Pin Buffer 18 Input

DAI Pin Buffer 20 Input

DAI_PB20_I_INVERT

DAI_PB19_I_INVERT

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...