ADSP-214xx SHARC Processor Hardware Reference A-155

Registers Reference

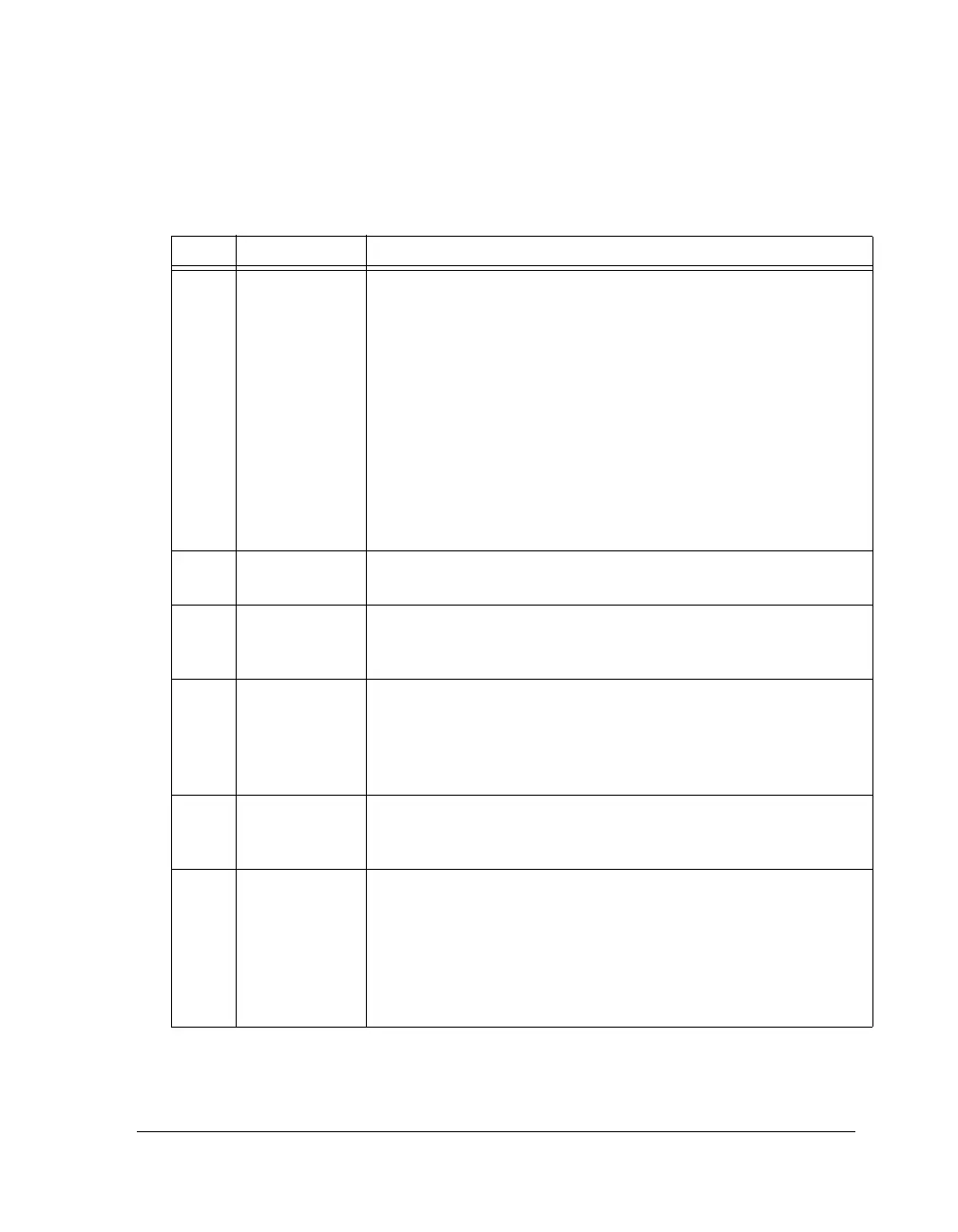

12 CKRE Clock Rising Edge Select. Determines clock signal to sample data and

the frame sync selection. For sampling receive data and frame syncs, set-

ting CKRE to 1 selects the rising edge of SPORTx_CLK. When CKRE

is cleared (=0), the processor selects the falling edge of SPORTx_CLK

for sampling receive data and frame syncs. Note that transmit data and

frame sync signals change their state on the clock edge that is not

selected.

For example, the transmit and receive functions of any two SPORTs

connected together should always select the same value for CKRE so

internally- generated signals are driven on one edge and received signals

are sampled on the opposite edge.

0 = Falling edge

1 = Rising edge

13 FSR Frame Sync Required Select. Selects whether the serial port requires (if

set, = 1) or does not require a transfer frame sync (if cleared, = 0).

14 IFS Internal Frame Sync Select. Selects whether the serial port uses an

internally generated frame sync (if set, = 1) or uses an external frame

sync (if cleared, = 0).

15 DIFS Data Independent Frame Sync Select.

1 = Serial port uses a data-independent frame sync (sync at selected

interval)

0 = Serial port uses a data-dependent frame sync (sync when TX FIFO

is not empty or when RX FIFO is not full).

16 LFS Active Low Frame Sync Select. This bit selects the logic level of the

(transmit or receive) frame sync signals. This bit selects an active low

frame sync (if set, = 1) or active high frame sync (if cleared, = 0).

17 LAFS Late Transmit Frame Sync Select. This bit selects when to generate the

frame sync signal. This bit selects a late frame sync if set (= 1) during

the first bit of each data word. This bit selects an early frame sync if

cleared (= 0) during the serial clock cycle immediately preceding the

first data bit

0 = Early frame sync (FS before first bit)

1 = Late frame sync (FS during first bit)

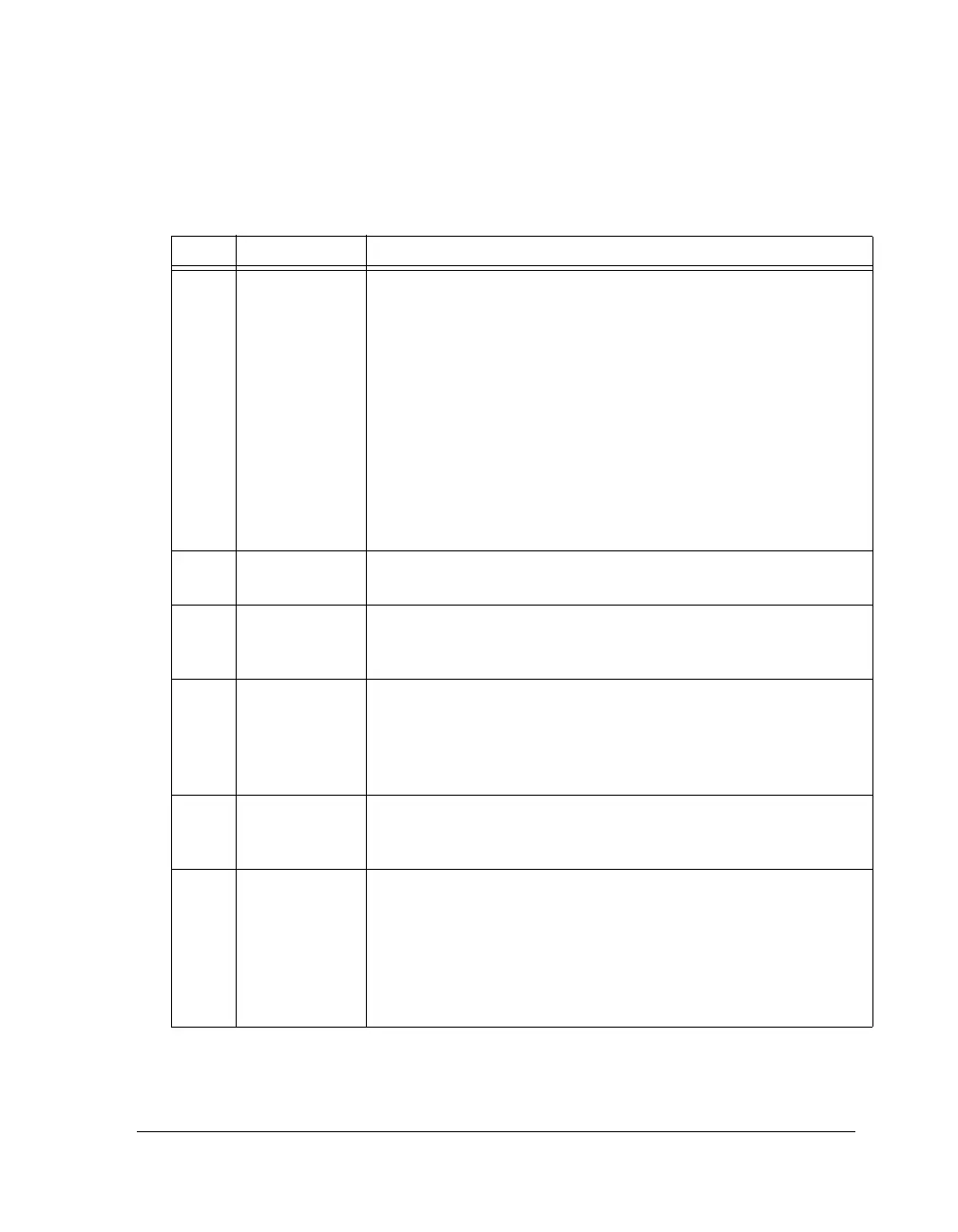

Table A-84. SPCTLx Register Bit Descriptions (Standard Serial Mode)

(RW) (Cont’d)

Bit Name Description

Loading...

Loading...