Peripherals Routed Through the DAI

A-156 ADSP-214xx SHARC Processor Hardware Reference

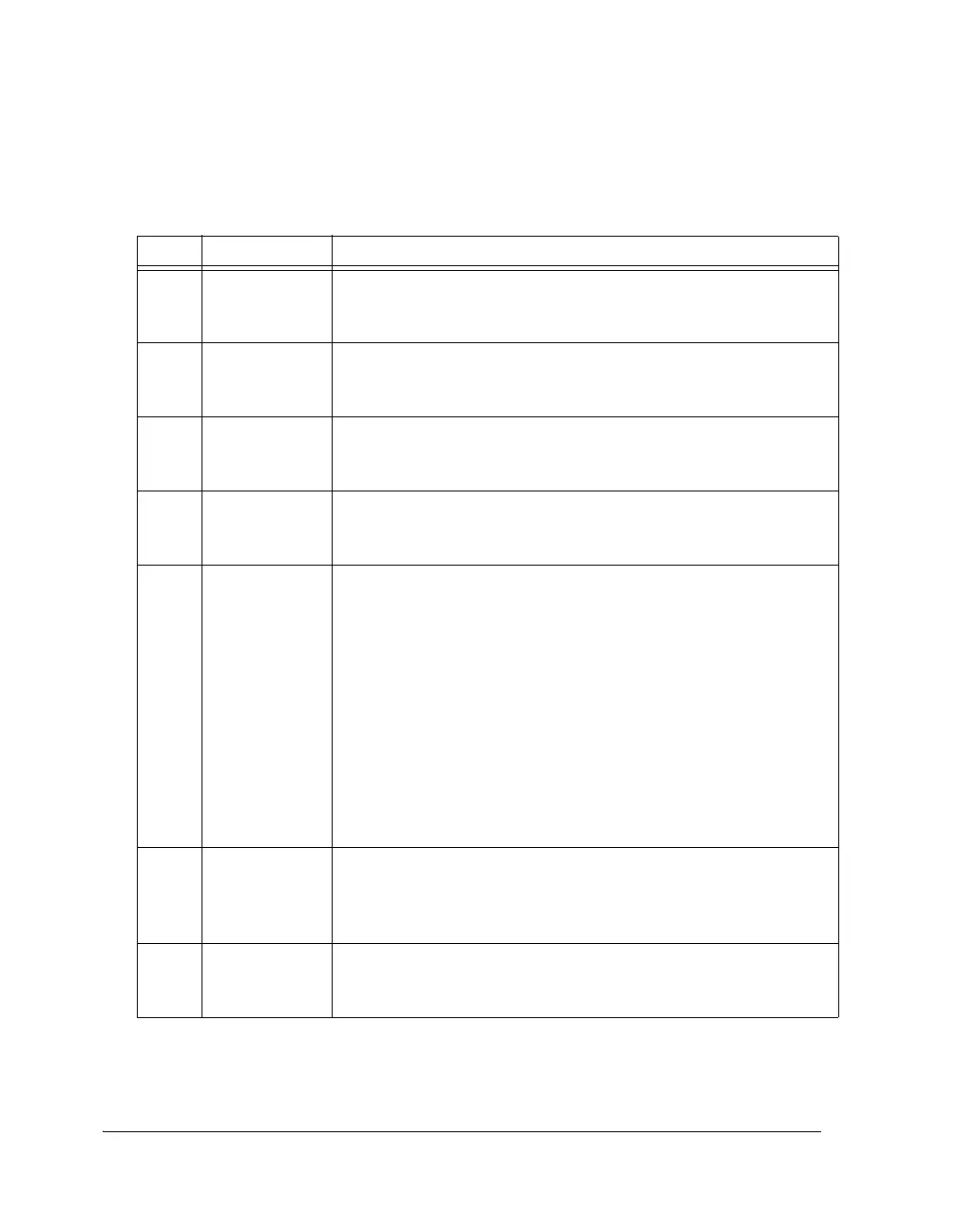

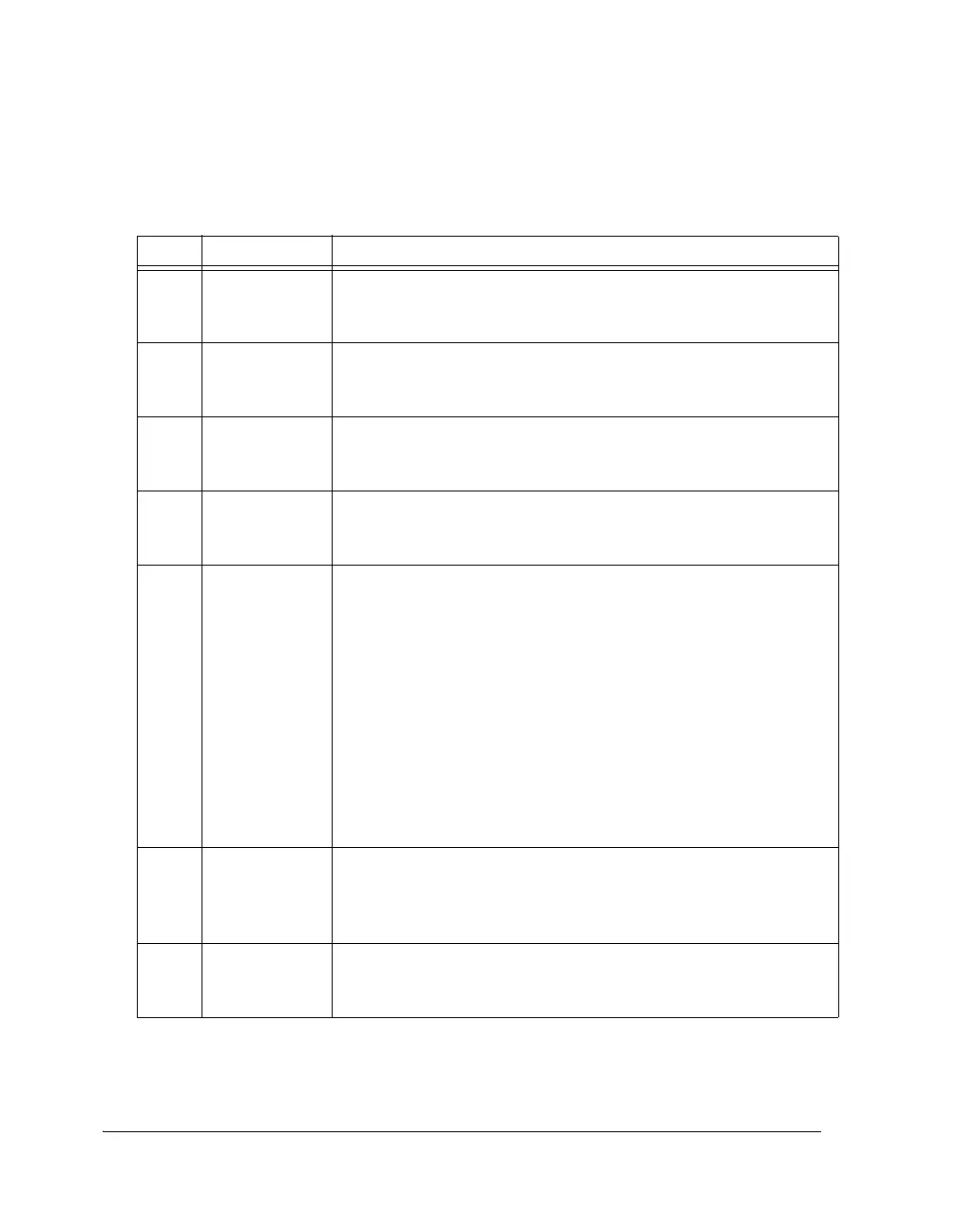

18 SDEN_A Enable Channel A Serial Port DMA.

0 = Disable serial port channel A DMA

1 = Enable serial port channel A DMA

19 SCHEN_A Enable Channel A Serial Port DMA Chaining.

0 = Disable serial port channel A DMA chaining

1 = Enable serial port channel A DMA chaining

20 SDEN_B Enable Channel B Serial Port DMA.

0 = Disable serial port channel B DMA

1 = Enable serial port channel B DMA

21 SCHEN_B Enable Channel B Serial Port DMA Chaining.

0 = Disable serial port channel B DMA chaining

1 = Enable serial port channel B DMA chaining

22 FS_BOTH FS Both Enable. This bit applies when the SPORTS channels A and B

are configured to transmit/receive data. If set (= 1), this bit issues frame

sync only when data is present in both transmit buffers, TXSPxA and

TXSPxB. If cleared (= 0), a frame sync is issued if data is present in

either transmit buffers.

When a SPORT is configured as a receiver, if FS_BOTH is set (= 1),

frame sync is issued only when both the RX FIFOs (RXSPxA and

RXSPxB) are not full.

If only channel A or channel B is selected, the frame sync behaves as if

FS_BOTH is cleared (= 0). If both A and B channels are selected, the

word select acts as if FS_BOTH is set (= 1).

0 = Issue FS if data is present in either transmit buffer.

1 = Issue FS if data is present in both transmit buffers.

23 BHD Buffer Hang Disable.

0 = Indicates a core stall. The core stalls when it tries to write to a full

transmit buffer or read an empty receive buffer FIFO.

1 = Ignore a core hang

24 SPEN_B Enable Channel B Serial Port.

0 = Serial port A channel disabled

1 = Serial port A channel enabled

Table A-84. SPCTLx Register Bit Descriptions (Standard Serial Mode)

(RW) (Cont’d)

Bit Name Description

Loading...

Loading...