ADSP-214xx SHARC Processor Hardware Reference A-157

Registers Reference

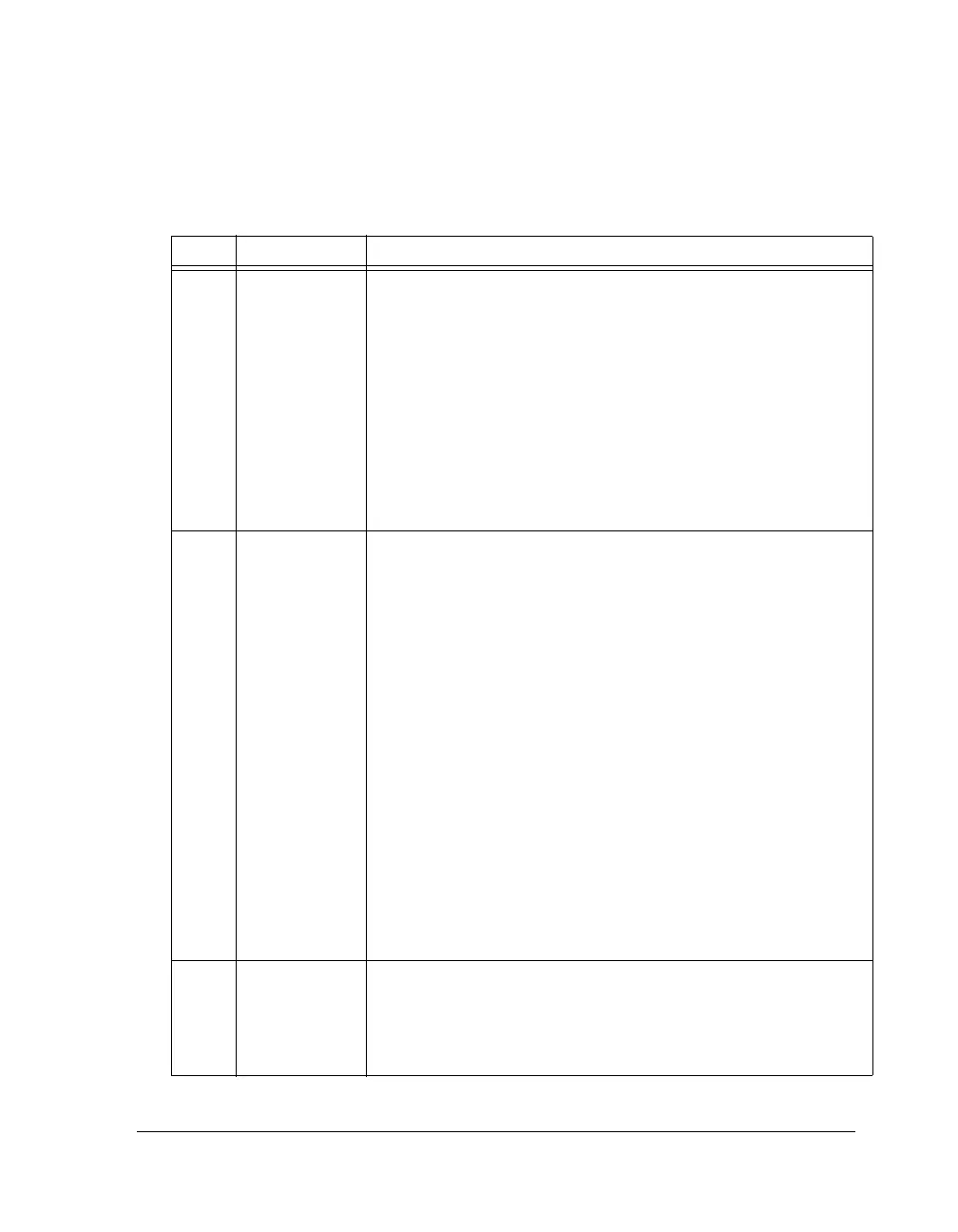

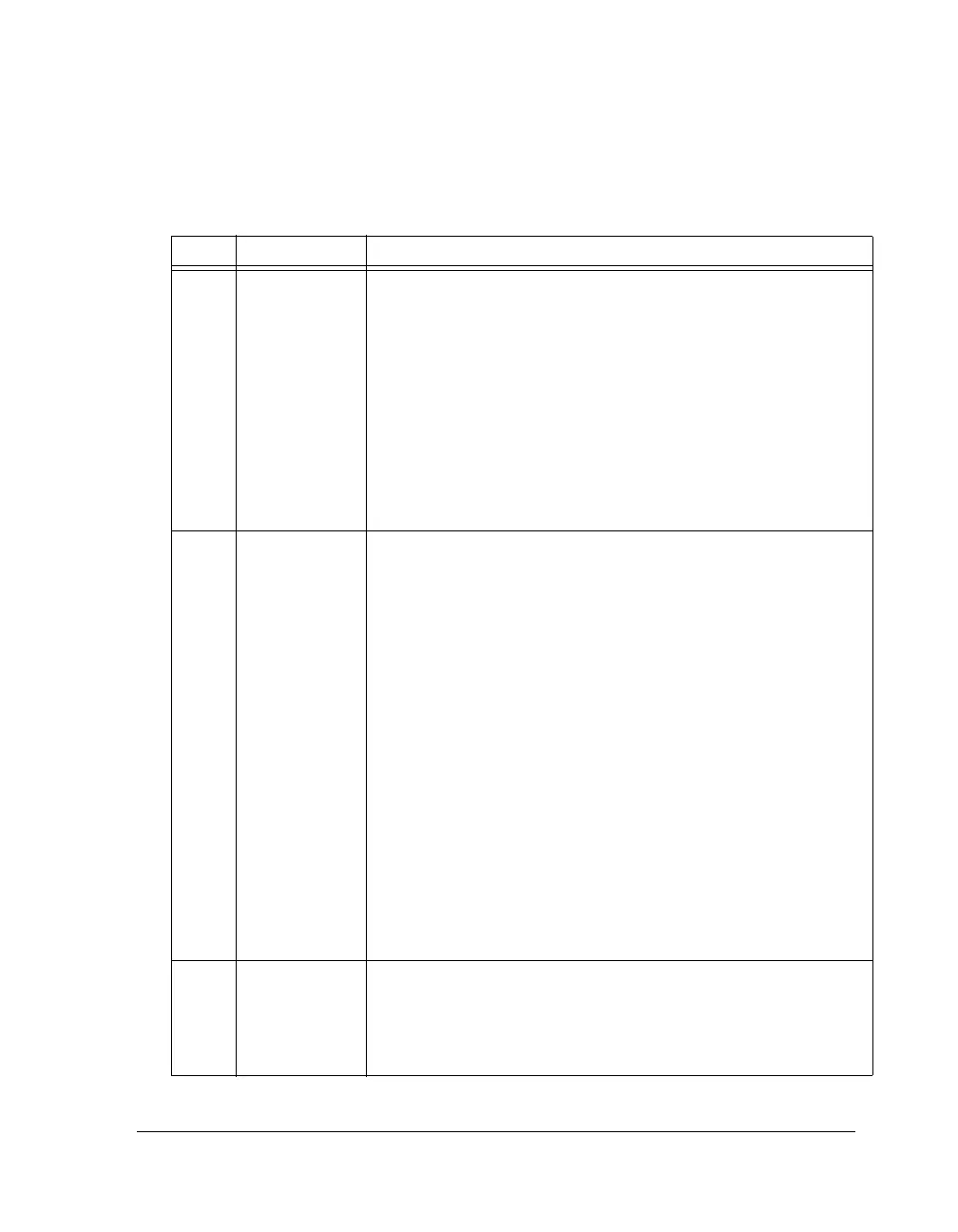

25 SPTRAN Data Direction Control. This bit controls the data direction of the

serial port channel A and B signals.

When cleared (= 0) the SPORT is configured to receive on both chan-

nels A and B. When configured to receive, the RXSPxA and RXSPxB

buffers are activated, while the receive shift registers are controlled by

SPORTx_CLK and SPORTx_FS. The TXSPxA and TXSPxB buffers

are inactive.

When set (= 1) the SPORT is configured to transmit on both channels

A and B. When configured to transmit, the TXSPxA and TXSPxB buf-

fers are activated, while the transmit shift registers are controlled by

SPORTx_CLK and SPORTx_FS. The RXSPxA and RXSPxB buffers

are inactive.

26

(RO)

DERR_B Channel B Error Status. When the SPORT is configured as a transmit-

ter, this bit provides transmit underflow status. If FSR = 1, DERR_x bit

indicates whether the SPORTx_FS signal (from an internal or external

source) occurred while the DXS_x buffer was empty. The SPORTs

transmit data whenever they detect a SPORTx_FS signal.

0 = No SPORTx_FS signal occurred while TXSPxA/B buffer is empty.

1 = SPORTx_FS signal occurred while TXSPxA/B buffer is empty.

If FSR = 0, DERR_x is set whenever the SPORT is required to transmit

and the transmit buffer is empty.

When the SPORT is configured as a receiver, this bit provides receive

overflow status. If FSR = 1, DERR_x bit indicates whether the

SPORTx_FS signal (from an internal or external source) occurred while

the DXS_x buffer was full. The SPORTs receive data whenever they

detect a SPORTx_FS signal. As a receiver, it indicates when the channel

has received new data while the receive buffer is full. New data over-

writes existing data.

0 = No SPORTx_FS signal occurred while RXSPxA/B buffer is full.

1 = SPORTx_FS signal occurred while RXSPxA/B buffer is full.

If FSR = 0, DERR_x is set whenever the SPORT is required to receive

and the receive buffer is full.

28–27

(RO)

DXS_B Channel B Data Buffer Status. Indicates the status of the serial port's

channel B data buffer (RXSPxB or TXSPxB) as follows:

00 = Empty

10 = Partially full

11 = Full

Table A-84. SPCTLx Register Bit Descriptions (Standard Serial Mode)

(RW) (Cont’d)

Bit Name Description

Loading...

Loading...