Peripherals Routed Through the DAI

A-158 ADSP-214xx SHARC Processor Hardware Reference

29

(RO)

DERR_A Channel A Error Status (sticky). Refer to DERR_B

31–30

(RO)

DXS_A Channel A Data Buffer Status. Refer to DXS_B

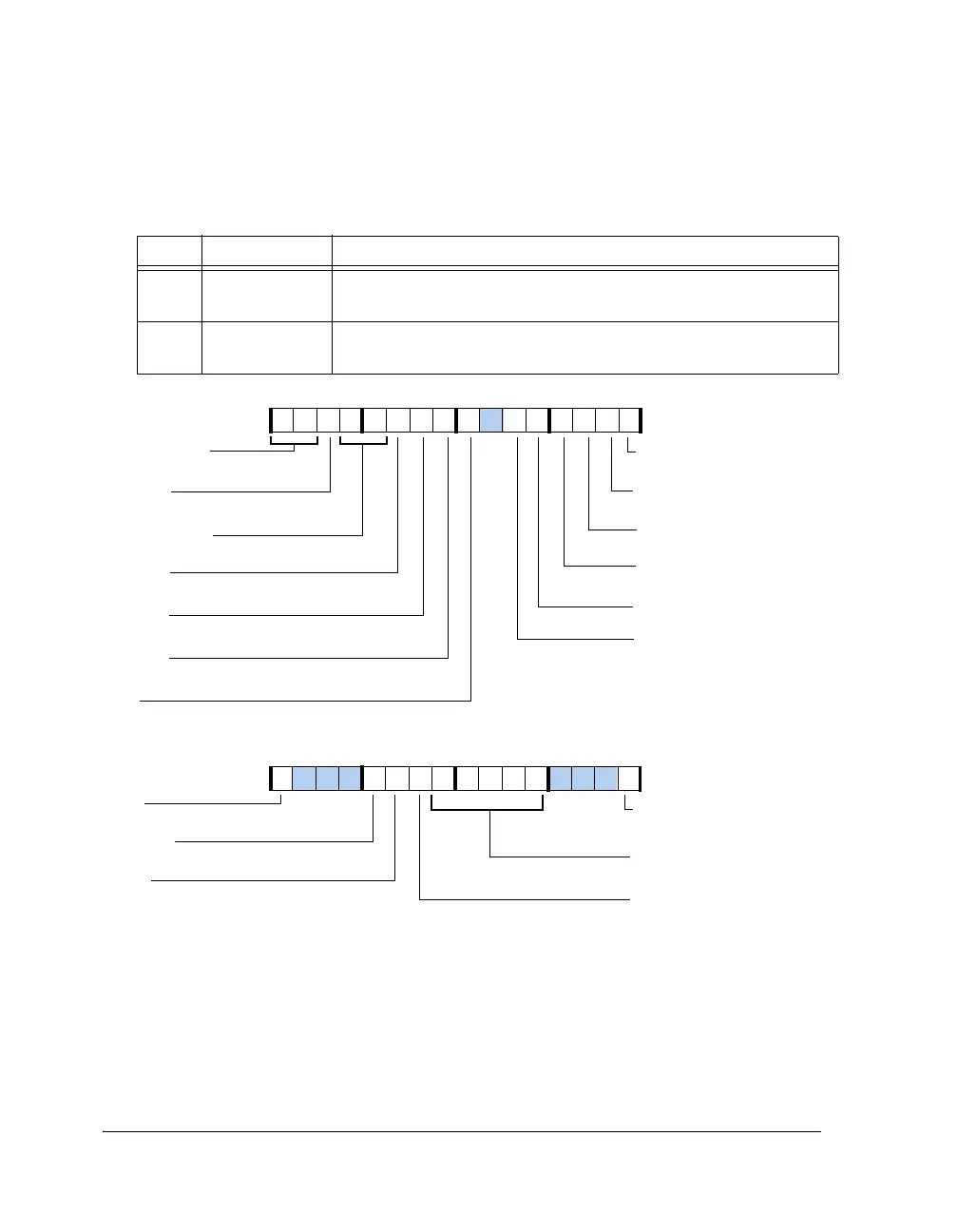

Figure A-87. SPCTLx Register for I

2

S and Left-Justified Modes

Table A-84. SPCTLx Register Bit Descriptions (Standard Serial Mode)

(RW) (Cont’d)

Bit Name Description

DXS_A (31–30)

Data Buffer Channel A Status

L_FIRST

Channel First Select

DERR_A

Channel A Error Status

SDEN_A

DMA Channel A Enable

DXS_B (28–27)

Data Buffer Channel B Status

DERR_B

Channel B Error Status

SPTRAN

SPORT Transaction

SPEN_B

SPORT Enable B

BHD

Buffer Hang Disable

LAFS

OPMODE

SCHEN_A

DMA Channel A Chaining Enable

SDEN_B

DMA Channel B Enable

SCHEN_B

DMA Channel B Chaining Enable

SPEN_A

DIFS

Data Independent Frame Sync

OPMODE

SPORT Operation Mode

MSTR

I

2

S Serial and L/R Clock Master

SPORT Enable A

SLEN (8–4)

Serial Word Length – 1

PACK

16/32 Packing

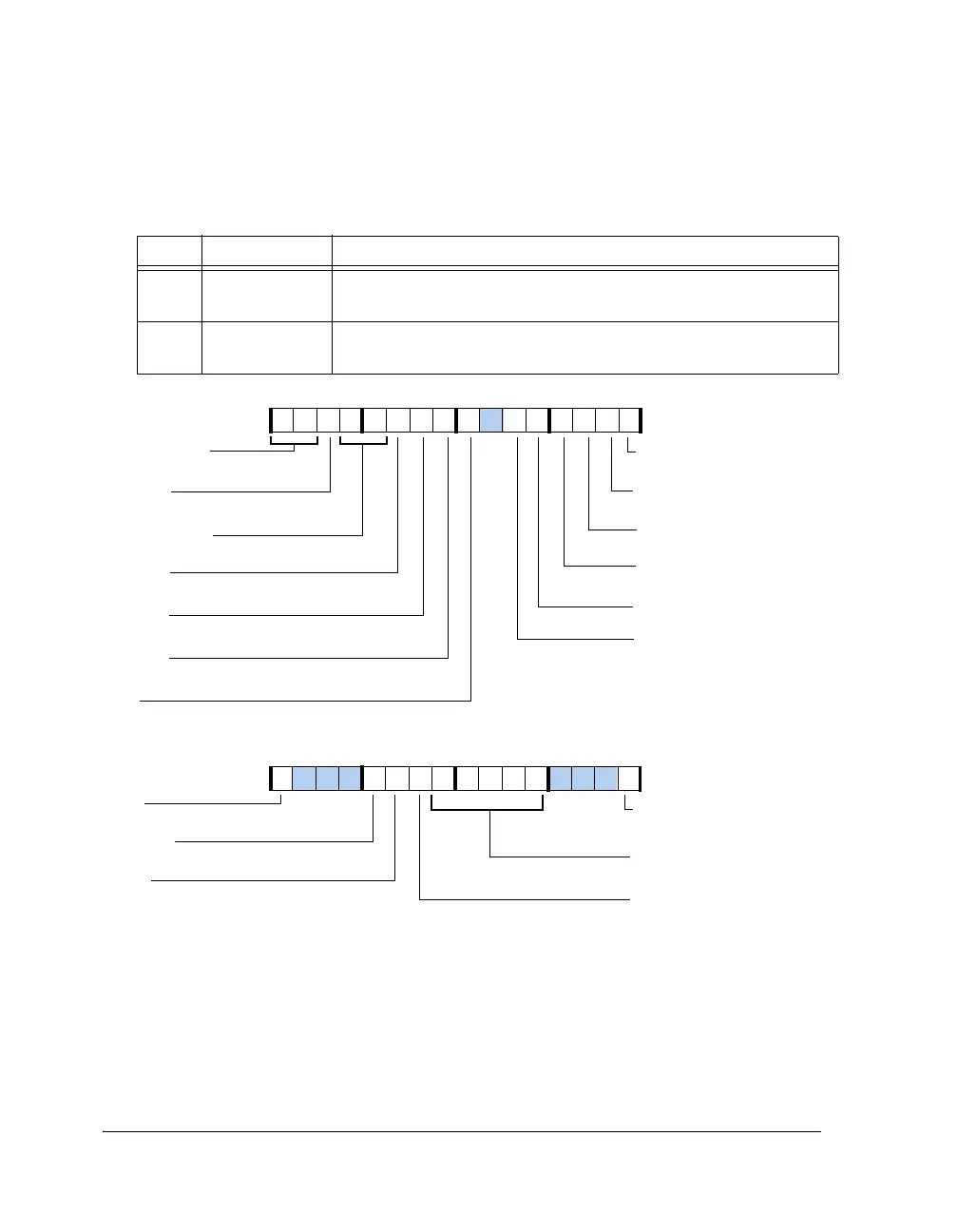

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...